|

|

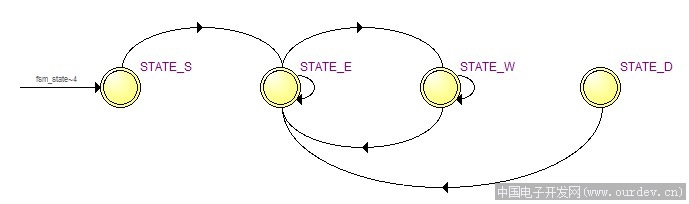

最近写一个状态机,出现了奇怪的问题,用quartus生成的状态图中可以看到有一个状态STATE_D无法跳转到。上图:

(原文件名:IncorrectFSM.jpg)

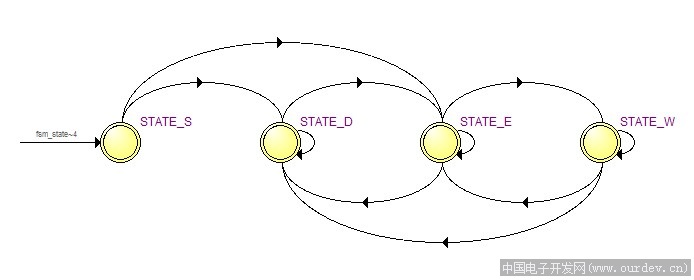

这是期望的状态图:

(原文件名:CorrectFSM.jpg)

代码如下:

module fsm(

mclk,

rst_n,

ein,

ain,

bout

);

input ain,ein,mclk,rst_n;

output bout;

reg bout;

reg[1:0] fsm_state;

parameter STATE_S = 2'b00;

parameter STATE_E = 2'b01;

parameter STATE_D = 2'b10;

parameter STATE_W = 2'b11;

//Bypass control state machine

always@(posedge mclk, negedge rst_n)

begin

if(!rst_n) begin

fsm_state <= STATE_S;

bout <= 1'b0;

end

else begin

case(fsm_state)

STATE_S:

begin

if(ein) begin

bout <= 1'b0;

fsm_state <= STATE_E;

end

else begin

bout <= 1'b1;

fsm_state <= STATE_D;

end

end

STATE_E:

begin

if(!ein) begin

bout <= 1'b1;

fsm_state <= STATE_D;

end

else if(ain) begin

bout <= 1'b1;

fsm_state <= STATE_W;

end

else begin

bout <= 1'b0;

fsm_state <= STATE_E;

end

end

STATE_D:

begin

if(ein) begin

bout <= 1'b0;

fsm_state <= STATE_E;

end

else begin

bout <= 1'b1;

fsm_state <= STATE_D;

end

end

STATE_W:

begin

if(!ein) begin

bout <= 1'b1;

fsm_state <= STATE_D;

end

else if(!ain) begin

bout <= 1'b0;

fsm_state <= STATE_E;

end

else begin

bout <= 1'b1;

fsm_state <= STATE_W;

end

end

default:

fsm_state <= STATE_S;

endcase

end

end

endmodule

很奇怪,倒不是写法的问题,不管用两个always、三个always的都一样,问题貌似和这个ein输入有关系。如果把ein改成两位的信号,或者把STATE_S处的ein改成!ein,都可以。难道是因为状态机里不允许出现“只要满足一个条件,任何状态都向某一个状态跳转”的情况吗?求教~~~~ |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|