|

|

很多资料都是这么写的:流水线处理是高速设计中的一个常用设计手段。如果某个设计的处理流程分为若干步骤,而且整个数据处理是“单流向”的,即没有反馈或者迭代运算,前一个步骤的输出是下一个步骤的输入,则可以考虑采用流水线设计方法来提高系统的工作频率。

想不明白为什么不能加反馈?

比如说:我要实现 C=A+B D=D+C ; 这算不算反馈呢?

代码:

module liushui

(

CLK,RSTn,A,B,C,D

);

input CLK;

input RSTn;

input [7:0] A;

input [7:0] B;

output [7:0] C;

output [7:0] D;

/***********************************************/

reg [7:0] rC;

reg [7:0] rD;

always@(posedge CLK or negedge RSTn)

if(!RSTn) begin

rC <= 8'd0;

rD <= 8'd0;

end

else begin

rC <= C;

rD <= D;

end

/***********************************************/

assign C = A + B;

assign D = rD + rC;

/***********************************************/

endmodule

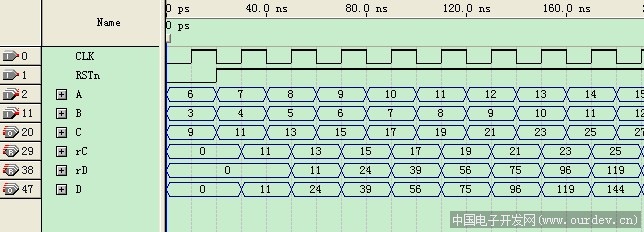

仿真:

(原文件名:fz.jpg)

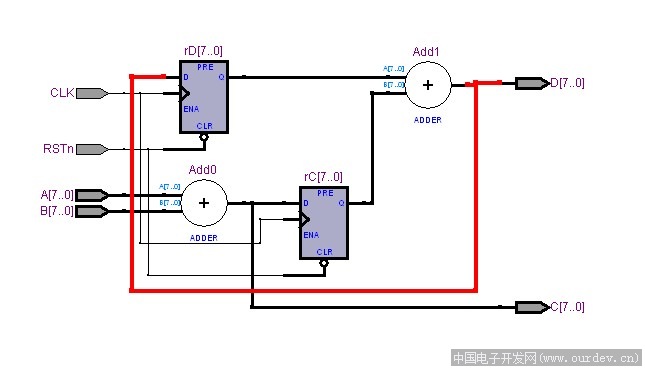

RTL:

(原文件名:zh.jpg) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|