|

|

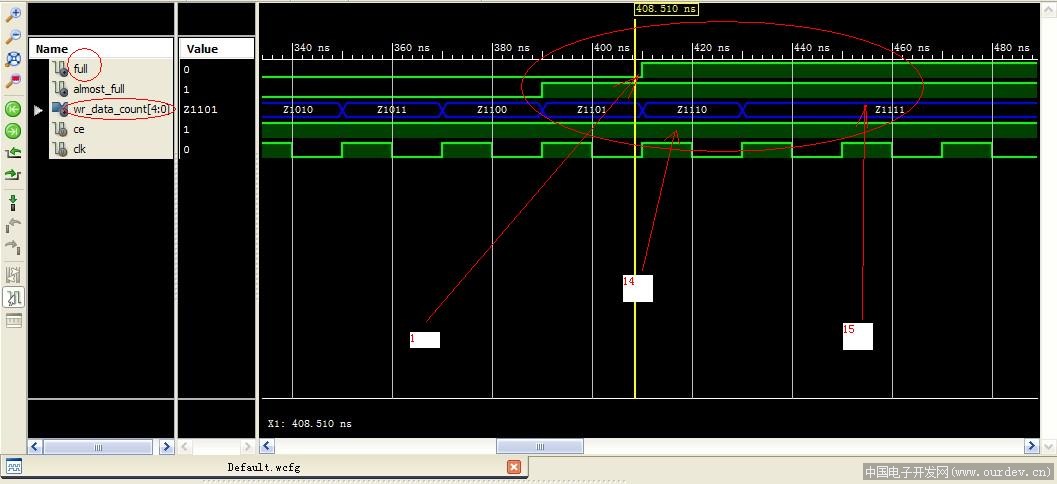

刚学习XILINX FIFO ,调用FIFO IP,数据宽度位16位,数据深度为16(实际为15),只写FIFO,不读FIFO。配置full、almost_full、wr_data_count 作为输出。

仿真波形如下。为什么full为1时写入个数为14 ? full=1后,可以继续写一个数据?按照我的理解,当出现full为1时,写入的数据的个数应该是15才对啊,而且之后不允许在写入数据吧?

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

module FIFOT(

ce,

clk,

full,

almost_full,

wr_data_count

);

input ce;

input clk;

output full;

output almost_full;

output[4:0] wr_data_count;

reg wr_en=0;

reg [15:0]din;

reg [4:0] counter=1;

always @(posedge clk)begin

if(ce==1)begin

wr_en<=1;

din<=counter;

end

end

fifo fifo1(

.wr_clk(clk), // input wr_clk

.rd_clk(rd_clk), // input rd_clk

.din(din), // input [15 : 0] din

.wr_en(wr_en), // input wr_en

.rd_en(), // input rd_en

.dout(), // output [15 : 0] dout

.full(full), // output full

.almost_full(almost_full), // output almost_full

.empty(), // output empty

.almost_empty(), // output almost_empty

.rd_data_count(), // output [3 : 0] rd_data_count

.wr_data_count(wr_data_count) // output [3 : 0] wr_data_count

);

endmodule

(原文件名:fifot.jpg)

仿真结果如上图。希望各位前辈不吝赐教,谢谢。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|