|

|

各位前辈好,小妹用eagle软件又遇到问题了,现在对brd文件中电压和涉及的电容连线这块很糊涂,特想前辈们讨教。

如题,设计的电路图需要对电路提供不同的电压,如+5V,-5V,0, 3.3V,2.5V,4.096V等。

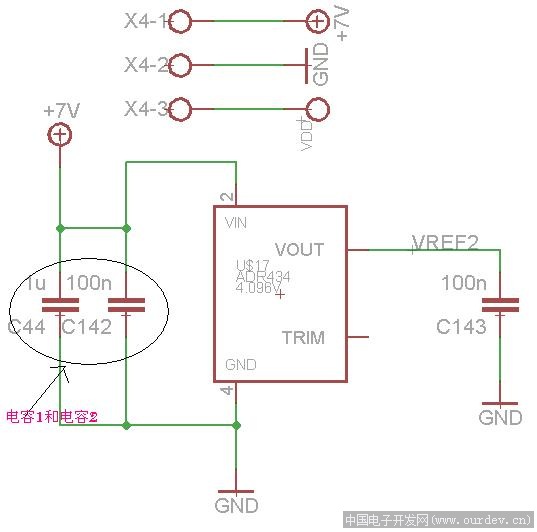

问题1: 现在在.sch电路图中已经把相对应的电源电路给定义好了,用+7Vsupply来生成参考电压4。096V,电路包括2个电容和一个ADR434(基准电压源),以得到4.096v的参考电压,如图1所示。

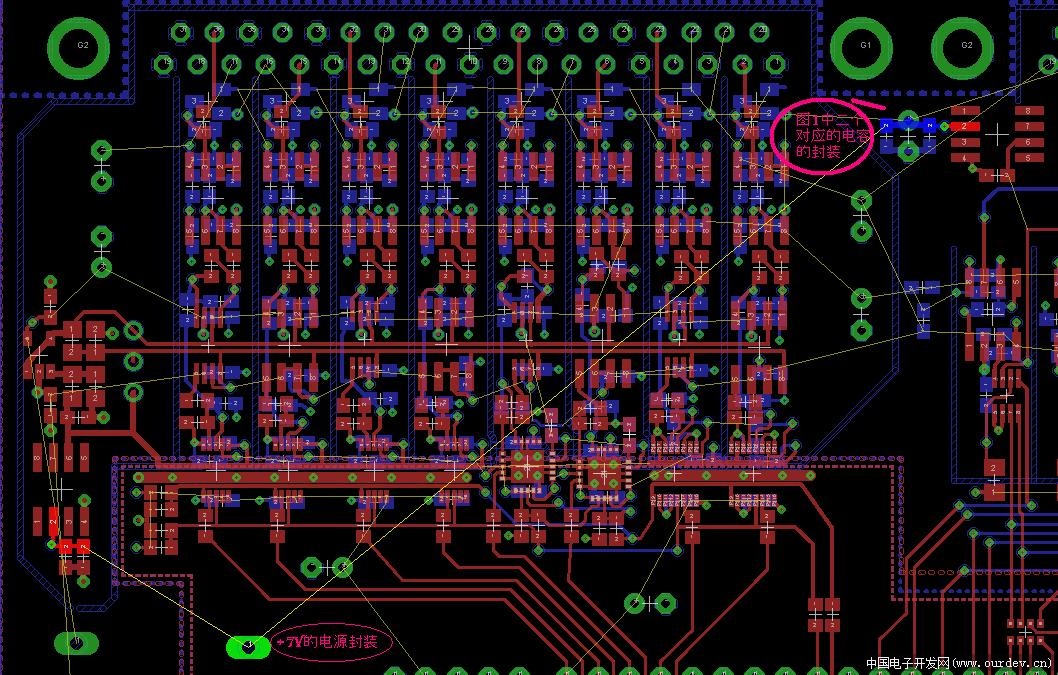

这样在.brd文件中,势必出现了电路中的2个电容和ADR434的封装, 我糊涂的是,在.brd文件中,自动出现了airwire,显示+7V的supply封装到2个电容

封装的连线。 这样的情况,我是不是需要用route命令把2者连起来? 这样2者离得非常远,连线很乱而且显的很傻,怎么处理呢?

问题2: 据我现在的理解,Polygon这个命令,也是在.brd文件中,对各个不同的电压,比如,+5,-5,+3.3V,GND,等的操作。 用Ploygon命令画好每一区块后,是不是直接定义好+3.3V就好,之后,区域内 所有显示+3.3V的airwire是不是就自动不显示了呢? 怎么样考虑哪个区块对应哪个电压呢?Polygon这命 令该怎么样理解啊?

问题3: 在.brd文件中, 元器件的某一个PIN角需要和+5V连结,用VIA命令 已经正确连接好了,但是为什么+5V的封装和已经连好+5V的PIN角之间的airwire仍然不消失呢。 怎么样消除这鼠线呢?

不知道我说清楚了没,此刻觉得语言太苍白啊。。。我还是先上几个截图,大家试着理解下。。。。非常非常非常感谢。。。。

图1 (原文件名:图1.JPG)

图2 (原文件名:图2.JPG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|