|

|

如题 Testbench代码如下

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--USE ieee.numeric_std.ALL;

ENTITY uart_bench IS

END uart_bench;

ARCHITECTURE behavior OF uart_bench IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT uart_top

PORT(

rs232_rx : IN std_logic;

rs232_tx : OUT std_logic;

clk : IN std_logic;

rst_n : IN std_logic

);

END COMPONENT;

--Inputs

signal rs232_rx : std_logic := '0';

signal clk : std_logic := '0';

signal rst_n : std_logic := '0';

--Outputs

signal rs232_tx : std_logic;

-- Clock period definitions

constant clk_period : time := 20 ns;

constant pbit_time : time := 104166 ns;

BEGIN

-- Instantiate the Unit Under Test (UUT)

uut: uart_top PORT MAP (

rs232_rx => rs232_rx,

rs232_tx => rs232_tx,

clk => clk,

rst_n => rst_n

);

stim_proc: process

begin

rst_n <= '1';

wait for 50 ns;

rst_n <= '0';

wait for 100 ns;

rst_n <= '1';

wait for 100*pbit_time;

end process;

process (clk,rst_n)

begin

IF rst_n = '0' THEN

clk <= '0';

-- rs232_rx <= '1';

ELSE

clk <= NOT clk AFTER 20 ns;

END IF;

end process;

process

begin

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '0';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '0';

wait for pbit_time;

rs232_rx <= '0';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '0';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '0';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

rs232_rx <= '1';

wait for pbit_time;

end process;

END;

是不是要把其它4个小模块给例化到Testbench中啊??? 多模块的联合仿真到底该怎么做啊???

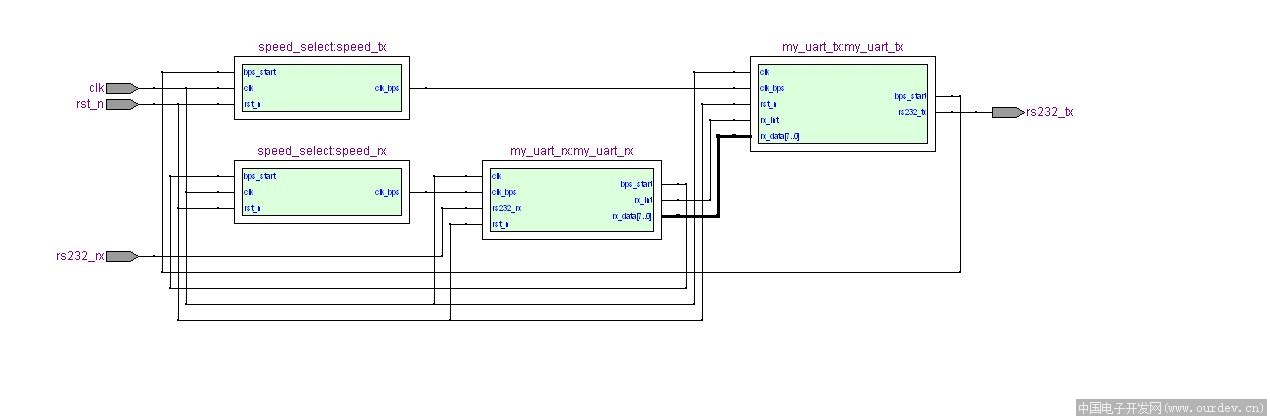

顶层模块图(源自特权_uart) (原文件名:my_uart_top.jpg)

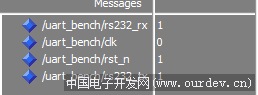

ModelsimSE中的信号列表 (原文件名:signal.png)

如图 怎么才能在ModelsimSE的信号列表中看到 bps_start,clk_bps,rx_int等这些中间信号?? |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|