|

|

楼主 |

发表于 2011-8-3 01:24:46

|

显示全部楼层

经测试,将“CHC_Compiler”添加到AD10.INI 文件中,然后生成的License文件可以激活CHC(用C语言设计FPGA)的功能。

================================================================================================================

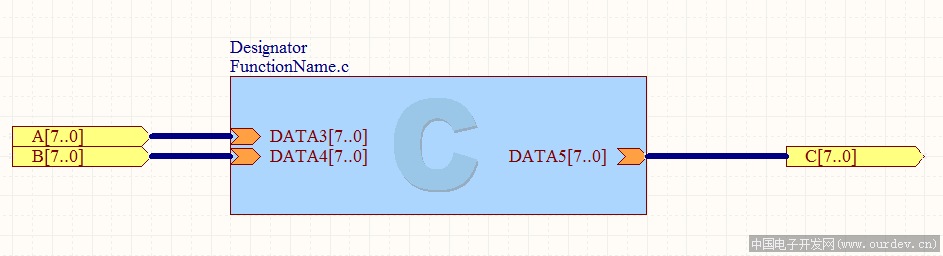

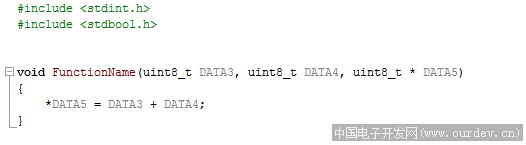

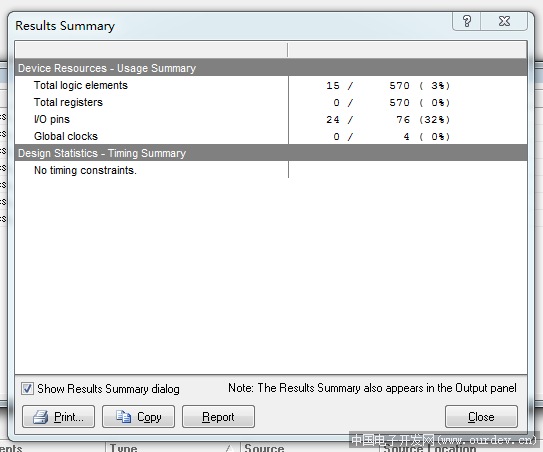

简单尝试一下加法运算。

(原文件名:1.PNG)

(原文件名:2.PNG)

(原文件名:4.PNG)

================================================================================================================

// TASKING HDL generator v1.3r1 Build 088

// options: -f ProjectOutputs\PCB Configuration\Main_Designator\Main_Designator.vhd.opt --toplevel=Main_Designator --wishbone-address-width=0 --wishbone-prefix= --vhdl=ProjectOutputs\PCB Configuration\Main_Designator\Main_Designator.vhd --verilog=ProjectOutputs\PCB Configuration\Main_Designator\Main_Designator.v

module Main_Designator

(

DATA3,

DATA4,

DATA5

);

input [7:0] DATA3;

input [7:0] DATA4;

output [7:0] DATA5;

wire [7:0] DATA3;

wire [7:0] DATA4;

wire [7:0] DATA5;

chc_Main_Designator_FunctionName FunctionName_0 (

.DATA5( DATA5 ),

.DATA3( DATA3 ),

.DATA4( DATA4 )

);

endmodule // Main_Designator

module chc_Main_Designator_ALU8

(

in0,

in1,

oper,

retval

);

input [7:0] in0;

input [7:0] in1;

input oper;

output [7:0] retval;

wire [7:0] in0;

wire [7:0] in1;

wire oper;

wire [7:0] retval;

assign retval = extract_8_9_8(({in0, oper} + {in1 ^ {8{oper}}, oper}));

function [7:0] extract_8_9_8;

input [8:0]x;

extract_8_9_8 = x[8:1];

endfunction

endmodule // chc_Main_Designator_ALU8

module chc_Main_Designator_FunctionName

(

DATA3,

DATA4,

DATA5

);

input [7:0] DATA3;

input [7:0] DATA4;

output [7:0] DATA5;

wire [7:0] ALU8_0_in0;

wire [7:0] ALU8_0_in1;

wire [7:0] ALU8_0_retval;

wire [7:0] DATA3;

wire [7:0] DATA4;

wire [7:0] DATA5;

wire [7:0] w1;

wire [7:0] w2;

wire [7:0] w3;

chc_Main_Designator_ALU8 ALU8_0 (

.in0( ALU8_0_in0 ),

.in1( ALU8_0_in1 ),

.retval( ALU8_0_retval ),

.oper( 1'b0 )

);

assign ALU8_0_in0 = DATA3;

assign ALU8_0_in1 = DATA4;

assign DATA5 = ALU8_0_retval;

endmodule // chc_Main_Designator_FunctionName

// end verilog |

|