|

|

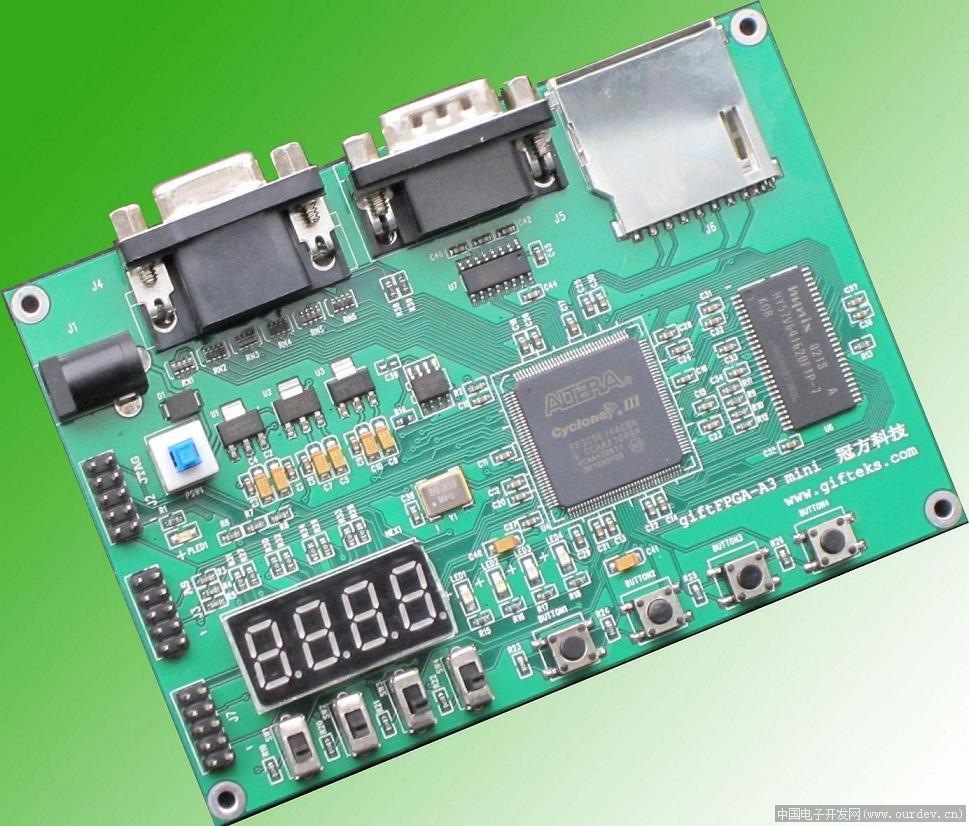

我所使用的芯片是Cyclone III EP3C5E144,与ep3c10e144是引脚兼容,没有去兼容ep3c16和25,因为用户IO相差太大,

本来qfp144的封装io就不太多,ep3c16和25就没有考虑。

ep3c5有5136个逻辑资源,跑普通的Verilog代码和niosII 完全足够了。

【参考资料】

建议大家在设计CylconeIII的板子时有几个文档是必看

1.Cyclone III Device Handbook

这个是CycloneIII 的官方手册,不必说,肯定是要看的

2.an466 Cyclone III Design Guidelines

这是Cyclone的设计指南,也很重要

3.Cyclone® III Device Family Pin Connection Guidelines

这个是引脚连接指南,设计硬件时最重要了,设计硬件的朋友一定多看几遍,特殊引脚如何处理上面都写清楚了

4...待续

【电源】

CycloneIII的最大不同就是增加了2.5v pll电压

只要记住一点就行 VCCA接2.5V ,VCCD_PLL接1.2V就行

一定记住VCCA是模拟电源,一定要用LDO啊

还有一个重要的就是qfp144封装的底部有一个接地焊盘,是必须要接地的。

先写到这、下次继续

<center> |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|