|

|

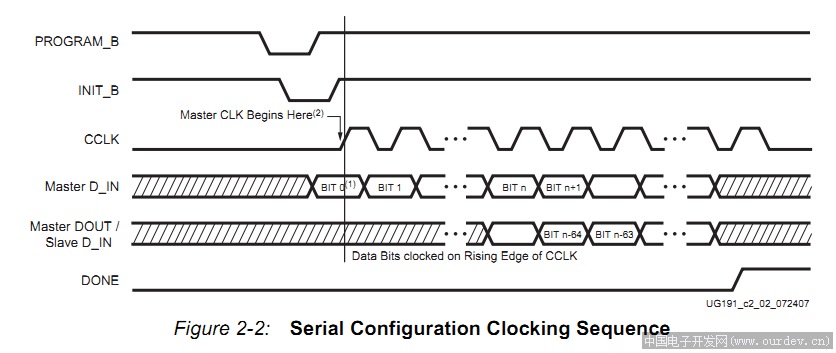

FPGA芯片为XC5VLX110T,ARM芯片为AT91SAM9G20,欲实现ARM对FPGA从串模式配置。FPGA从串模式配置流程如下:

(原文件名:sequence.png)

实现流程如下:

首先,将ARM程序、FPGA程序下载到外部Dataflash(Atmel公司)中;

然后,在ARM的bootstrap程序中,将两部分程序都搬运到SDRAM中;

再次,在ARM裸机程序中,读取SDRAM相应地址的值(即FPGA程序),以串行的方式送入FPGA中;

问题如下:

1、在读取SDRAM中一字节后,无论先传高位和地位,FPGA内部校验始终不会出错;

2、配置数据结束,DONE管脚始终为低,不会变高;

不知道问题出在哪儿?求高人指教!

配置程序流程如下:

Pin PinsFpga[5] = {PIN_FPGA_PROG_B, PIN_FPGA_CCLK, PIN_FPGA_D_IN, PIN_FPGA_DONE, PIN_FPGA_INIT_B};//配置相关引脚声明

PIO_Configure(PinsFpga, 5);

//generate a low pulse on PROG_B

PIO_Clear(&PinsFpga[FPGA_PROG_B]);

//wait INIT_B goes low

while(1 == PIO_Get(&PinsFpga[FPGA_INIT_B]));

//pull up the PROG_B port, start the configuration process

PIO_Set(&PinsFpga[FPGA_PROG_B]);

//wait INIT_B goes high, indicating that the FPGA is ready to receive configuration data

while(0 == PIO_Get(&PinsFpga[FPGA_INIT_B]));

PIO_Clear(&PinsFpga[FPGA_CCLK]);

delay(300);

//begin to send the FPGA configuration data

pConfigData = (unsigned char *)FPGA_CONFIG_DATA_ADDR;//SDRAM中存储FPGA 程序起始地址

for(i=0; i<FPGA_CONFIG_DATA_LEN; i++)//FPGA_CONFIG_DATA_LEN 是 FPGA程序固定长度

{

data =*(pConfigData+i);

for(j=0; j<8; j++)

{

if(data & (unsigned char)0x01<<j)

{

PIO_Set(&PinsFpga[FPGA_D_IN]);

}

else

{

PIO_Clear(&PinsFpga[FPGA_D_IN]);

}

PIO_Set(&PinsFpga[FPGA_CCLK]);

PIO_Clear(&PinsFpga[FPGA_CCLK]);

}

if(0 == i%CHECK_EVERY_X_BYTE)//判断INIT_B的状态,若为低,出错退出;若为高,不出错,继续。

{

//Check INIT_B

if(0 == PIO_Get(&PinsFpga[FPGA_INIT_B]))

{

return FALSE;

}

}

}

//delay for 10us to wait for the DONE goes to high

delay(10);

//Toggle CCLK for INIT_CYCLE cycles

for(i=0; i<8; i++)//INIT_CYCLE

{

PIO_Set(&PinsFpga[FPGA_CCLK]);

PIO_Clear(&PinsFpga[FPGA_CCLK]);

}

if(0 == PIO_Get(&PinsFpga[FPGA_DONE]) || 0 == PIO_Get(&PinsFpga[FPGA_INIT_B]))

{

return FALSE;

} |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|