|

|

楼主 |

发表于 2011-5-18 15:44:04

|

显示全部楼层

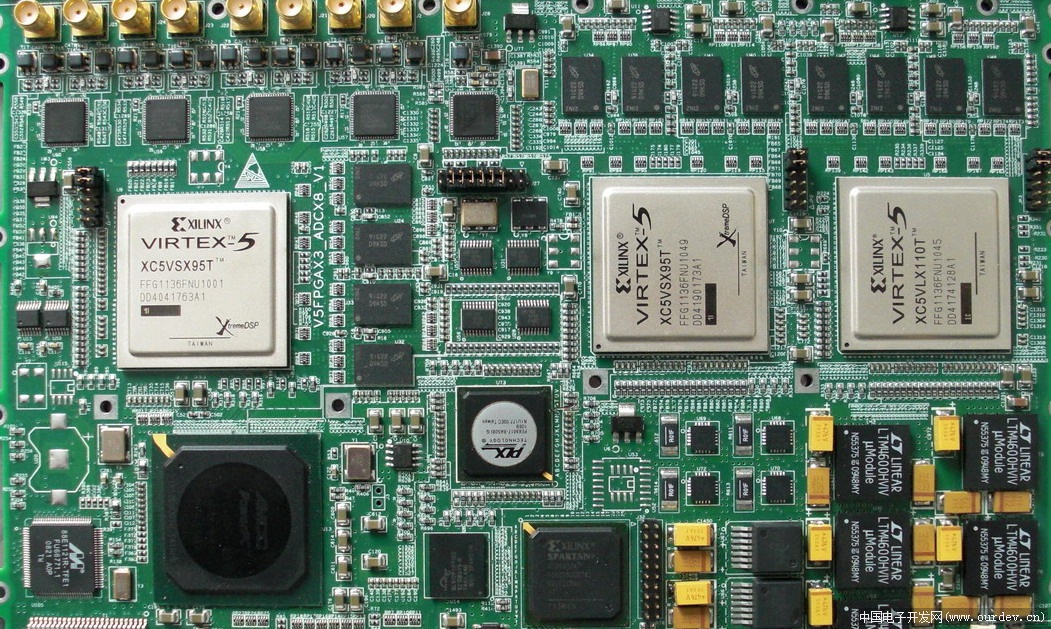

最近忙1个3FPGA,2个CameraLINK FPGA板子,前后忙了6个月,没来得发帖。准备最近发发。。。

现在3FPGA板子我这部分(原理/加电/初测)结束,转给别人调了。

(原文件名:fpga_x3_s.jpg)

UBOOT一下子扫到这么多PCIE设备,很满足:

512 MB (ECC not enabled, 400 MHz, CL3)

Top of RAM usable for U-Boot at: 20000000

Reserving 668k for U-Boot at: 1ff58000

Reserving 1040k for malloc() at: 1fe54000

Reserving 160 Bytes for Board Info at: 1fe53f60

Reserving 56 Bytes for Global Data at: 1fe53f28

Stack Pointer at: 1fe53f08

New Stack Pointer is: 1fe53f08

Now running in RAM - U-Boot at: 1ff58000

FLASH: 64 MB

NAND: 0 MiB

PCI: Bus Dev VenId DevId Class Int

PCIE1: successfully set as root-complex

04 00 10ee 0007 0580 ff

03 00 10b5 8617 0604 00

05 00 10ee 0007 0580 ff

03 01 10b5 8617 0604 00

06 00 10ee 0007 0580 ff

03 03 10b5 8617 0604 00

02 00 10b5 8617 0604 00

U-Boot relocated to 1ff58000

DTT: 1 is 32 C

DTT: 2 is 44 C

DTT: 3 is 32 C

DTT: 4 is 35 C

DTT: 5 is 33 C

DTT: 6 is 36 C

DTT: 7 is 33 C

DTT: 8 is 35 C

Net: ppc_4xx_eth0, ppc_4xx_eth1

VXWORKS下也扫到。。。

-> pciDeviceShow 1

Scanning function 0 of each PCI device on bus 1

Using configuration mechanism 0

bus device function vendorID deviceID class

00000001 00000000 00000000 000010b5 00008617 00060400

value = 0 = 0x0

-> pciDeviceShow 2

Scanning function 0 of each PCI device on bus 2

Using configuration mechanism 0

bus device function vendorID deviceID class

00000002 00000000 00000000 000010b5 00008617 00060400

00000002 00000001 00000000 000010b5 00008617 00060400

00000002 00000003 00000000 000010b5 00008617 00060400

value = 0 = 0x0

-> pciDeviceShow 3

Scanning function 0 of each PCI device on bus 3

Using configuration mechanism 0

bus device function vendorID deviceID class

00000003 00000000 00000000 000010ee 00000007 00058000

value = 0 = 0x0

-> pciDeviceShow 4

Scanning function 0 of each PCI device on bus 4

Using configuration mechanism 0

bus device function vendorID deviceID class

00000004 00000000 00000000 000010ee 00000007 00058000

value = 0 = 0x0

-> pciDeviceShow 5

Scanning function 0 of each PCI device on bus 5

Using configuration mechanism 0

bus device function vendorID deviceID class

00000005 00000000 00000000 000010ee 00000007 00058000

value = 0 = 0x0 |

|