|

|

(1)assign readdata = {2{{address == 0}}} && out_data;

(2)assign readdata = (address == 0) ? out_data : 0;

这两句话有什么区别吗???

当address = 0 的时候,readdata = 2’b11 && out_data = out_data; 两式一样

当address != 0 的时候,readdata = 2’b00 && out_data = 0; 两式还是一样

“时间是检验真理的唯一标准”,用verilog RTL测试

(1)

module verilog_test

(

input [1:0] address,

input [1:0] out_data,

output [1:0] readdata

);

assign readdata = {2{{address == 0}}} && out_data;

endmodule

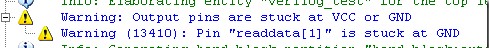

出现了这样的警告

(原文件名:1.jpg)

这不现实啊,

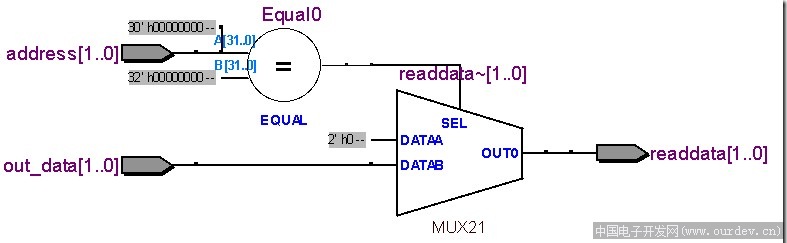

RTL如下:

(原文件名:2.jpg)

看不太懂!!!

(2)

module verilog_test

(

input [1:0] address,

input [1:0] out_data,

output [1:0] readdata

);

assign readdata = (address == 0) ? out_data : 0;

endmodule

这个没那个高位始终为0的警告,出来的效果也是我们可想而知的,RTL如下

(原文件名:3.jpg)

可这是为什么捏??不应该一样的吗???

顺便说下,当然RTL绝对不可能是一样的,一个是与门 一个是选择器,但是出现readdata 高位始终为0,这个实在想不通 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|