|

|

最近在调DAC_TLC5615想请教下各位前辈一些问题?

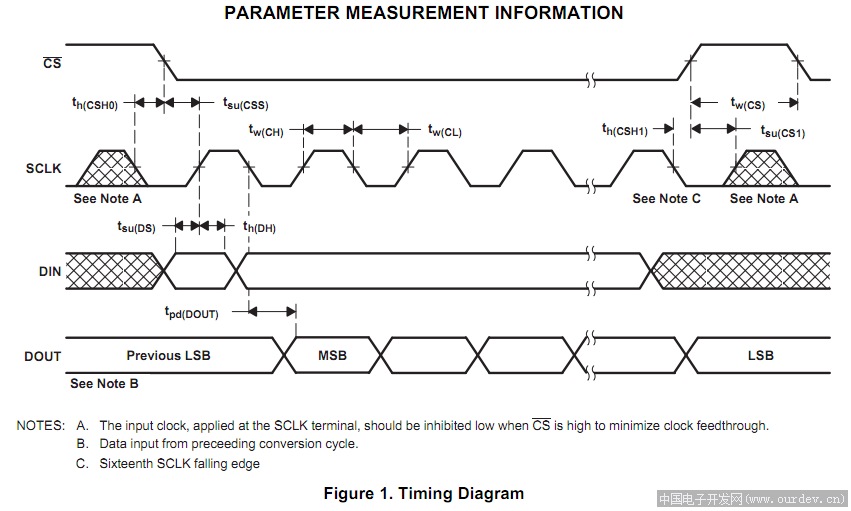

首先我先上时序图

TLC时序图 (原文件名:TLC5615_timing_diagram.png)

问题1:

时序图中的note1提到:为了使时钟馈通为最小,当CS为高电平时加在SCLK端的输入时钟应当呈现低电平。为何时序图中sclk的状态是无关表示呢?(头和尾)

问题2:

noteA对应时钟的后一个时钟对应的那一小段din是不是数据建立的过程?真正开始数据打入DAC移位register是还要再后一个时钟开始呢?

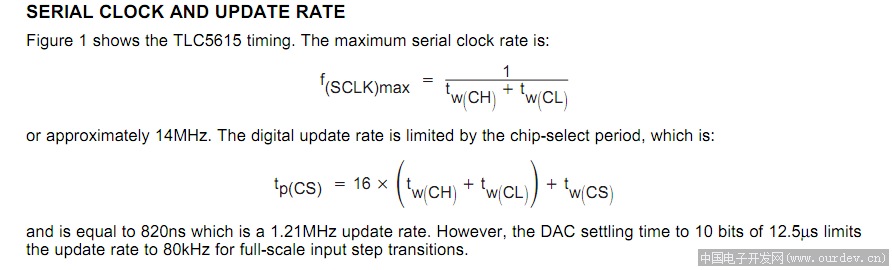

再上时钟速率图

(原文件名:时钟速率.png)

问题3:

(关于最大串行时钟速率)

由时序图可知Tw(CH)和Tw(CL)各为25ns理应sclk为20Mhz,但时钟都会有一定的倾斜,并不是理想的是陡峭的上升沿和下降沿,时序图中示出的仅是sclk高电平和低电平稳定的时间,sclk变化也会有一定的时间,即倾斜部分,因此近似为14Mhz.这样解释对吗?

问题4:

数字更新速率,等于820ns为1.21Mhz这个是不是也是理想的计算值因为他好像没考虑时钟的倾斜?还有后面的那句话,对于满度输入阶跃跳变,10位DAC建立时间为12.5μs,这把更新速率限制至80kHz,这句话该怎么理解呢?满度输入阶跃跳变是什么意思哦? 后面的10位DAC建立时间为12.5us是怎么算出来的呢?

问题比较多。。麻烦各位前辈了。。。真心请教。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|