|

|

发表于 2011-4-19 16:40:56

|

显示全部楼层

发表于 2011-4-19 16:40:56

|

显示全部楼层

【42楼】 RENMA

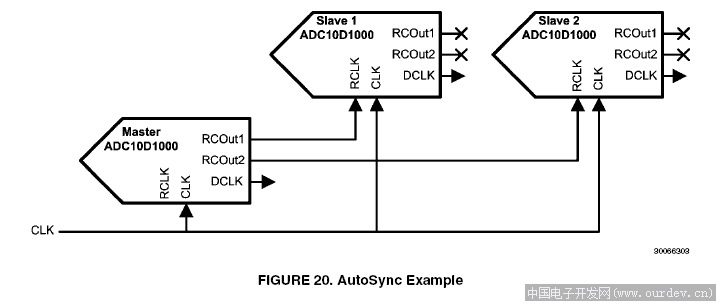

17.4 SYNCHRONIZING MULTIPLE ADC10D1000/1500S IN A SYSTEM

The ADC10D1000/1500 has two features to assist the user with synchronizing multiple ADCs in a system; AutoSync and

DCLK Reset. The AutoSync feature is new and designates

one ADC10D1000/1500 as the Master ADC and other

ADC10D1000/1500s in the system as Slave ADCs. The

DCLK Reset feature performs the same function as the AutoSync

feature, but is the first generation solution to synchronizing

multiple ADCs in a system; it is disabled by default. For

the application in which there are multiple Master and Slave

ADC10D1000/1500s in a system, AutoSync may be used to

synchronize the Slave ADC10D1000/1500(s) to each respective

Master ADC10D1000/1500 and the DCLK Reset may be

used to synchronize the Master ADC10D1000/1500s to each

other.

17.4.1 AutoSync Feature

AutoSync is a new feature which continuously synchronizes

the outputs of multiple ADC10D1000/1500s in a system. It

may be used to synchronize the DCLK and data outputs of

one or more Slave ADC10D1000/1500s to one Master ADC10D1000/

1500. Several advantages of this feature include:

no special synchronization pulse required, any upset in synchronization

is recovered upon the next DCLK cycle, and the

Master/Slave ADC10D1000/1500s may be arranged as a binary

tree so that any upset will quickly propagate out of the

system.

An example system is shown below in Figure 20 which consists

of one Master ADC and two Slave ADCs. For simplicity,

only one DCLK is shown; in reality, there is DCLKI and

DCLKQ, but they are always in phase with one another.

In order to synchronize the DCLK (and Data) outputs of multiple

ADCs, the DCLKs must transition at the same time, as

well as be in phase with one another. The DCLK at each ADC

is generated from the CLK after some latency, plus tOD minus

tAD. Therefore, in order for the DCLKs to transition at the same

time, the CLK signal must reach each ADC at the same time.

To tune out any differences in the CLK path to each ADC, the

tAD adjust feature may be used. However, using the tAD adjust

feature will also affect when the DCLK is produced at the output.

If the device is in Demux Mode, then there are four

possible phases which each DCLK may be generated on because

the typical CLK = 1GHz and DCLK = 250 MHz for this

case. The RCLK signal controls the phase of the DCLK, so

that each Slave DCLK is on the same phase as the Master

DCLK.

The AutoSync feature may only be used via the Control Registers.

(原文件名:1.JPG) |

|