|

|

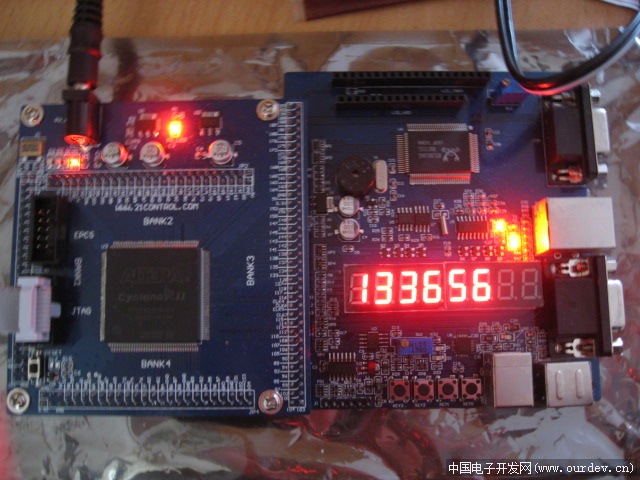

学FPGA的第一个作品~ 钟。。。 功能简单, 时分秒数码管动态显示, 两个按键修改时、分数值。

直接上代码~ 觉得好的可以拿去,觉得不好的,强烈欢迎批评~ 谢谢

补充图片

相机不是很好~ (原文件名:IMG_0127.JPG)

module lednum(clk,rst,key,secled,sledccom,sleddata);

input clk;

input rst;

input [1:0] key;

output secled;

output[7:0] sleddata;

output[7:0] sledccom;

//***********50MHZ->2HZ*********************

reg[18:0] fcout;

reg[18:0] scout;

reg secled;

always@(posedge clk)

begin

fcout<=fcout+19'd1;

end

always@(posedge fcout[5])

begin

if(scout==19'd390624) //50,000,000/2^(5+1)/(390624+1)=2

begin

scout=0;

secled=~secled;

end

else

scout=scout+19'd1;

end

//**********Read KEYs***********************

reg [2:0] kcout0,kcout1;

reg keyout0,keyout1;

always@(posedge fcout[17]) //KEY1

begin

if(key[0])

begin

kcout0=0;

keyout0=1;

end

else if(kcout0==3'd4)

keyout0=0;

else

kcout0=kcout0+3'd1;

end

always@(posedge fcout[17]) //KEY2

begin

if(key[1])

begin

kcout1=0;

keyout1=1;

end

else if(kcout1==3'd4)

keyout1=0;

else

kcout1=kcout1+3'd1;

end

//************SEC*********************

reg[3:0]secg;

reg[3:0]secs;

reg sec_c;

wire min_plus;

always@(negedge secled or negedge rst)

begin

if(!rst)

begin

secg=0;

secs=0;

end

else

begin

if(secg==4'd9)

begin

secg=0;

if(secs==4'd5)

begin

secs=0;

sec_c=0;

end

else

begin

secs=secs+4'd1;

sec_c=1;

end

end

else

begin

secg=secg+4'd1;

sec_c=1;

end

end

end

assign min_plus=sec_c&keyout0;

//************MIN********************

reg[3:0]ming;

reg[3:0]mins;

reg min_c;

wire hour_plus;

always@(negedge min_plus or negedge rst)

begin

if(!rst)

begin

ming=0;

mins=0;

end

else

begin

if(ming==4'd9)

begin

ming=0;

if(mins==4'd5)

begin

mins=0;

min_c=0;

end

else

begin

mins=mins+4'd1;

min_c=1;

end

end

else

begin

ming=ming+4'd1;

min_c=1;

end

end

end

assign hour_plus=min_c&keyout1;

//***************HOUR*****************

reg[3:0]hourg;

reg[3:0]hours;

always@(negedge hour_plus or negedge rst)

begin

if(!rst)

begin

hourg=2;

hours=1;

end

else

begin

if(hourg==4'd9)

begin

hourg=0;

hours=hours+4'd1;

end

else if((hourg==4'd3)&(hours==4'd2))

begin

hourg=0;

hours=0;

end

else

hourg=hourg+4'd1;

end

end

//*************SHOW**************************

reg[7:0] sleddata;

reg[7:0] sledccom;

reg[3:0] showbuff;

always@(posedge fcout[16])

begin

case(sledccom)

8'b11111011:begin

sledccom<=8'b01111111;

showbuff<=hours; //hours

end

8'b01111111:begin

sledccom<=8'b10111111;

showbuff<=hourg; //hourg

end

8'b10111111:begin

sledccom<=8'b11011111;

showbuff<=mins; //mins

end

8'b11011111:begin

sledccom<=8'b11101111;

showbuff<=ming; //ming

end

8'b11101111:begin

sledccom<=8'b11110111;

showbuff<=secs; //secs

end

8'b11110111:begin

sledccom<=8'b11111011;

showbuff<=secg; //secg

end

/*

8'b11111011:begin

sledccom<=8'b11111101;

showbuff<=tbuff1; //tbuff1

end

8'b11111101:begin

sledccom<=8'b11111110;

showbuff<=tbuff1; //tbuff2

end

*/

default :sledccom<=8'b11111011;

endcase

end

always@(sledccom or showbuff) //num->7seg

begin

case(showbuff)

4'd0:sleddata=8'hc0;//0

4'd1:sleddata=8'hf9;//1

4'd2:sleddata=8'ha4;//2

4'd3:sleddata=8'hb0;//3

4'd4:sleddata=8'h99;//4

4'd5:sleddata=8'h92;//5

4'd6:sleddata=8'h82;//6

4'd7:sleddata=8'hf8;//7

4'd8:sleddata=8'h80;//8

4'd9:sleddata=8'h90;//9

default:sleddata=8'hff;

endcase

end

endmodule

//***************************END**********************************

目前的BUG是当 秒或分为0时,无法修改 分和时的数值, 还在思考中, 弄完这个,下一个目标是做一个RS232串口,让单片机并行写入读出,FPGA处理协议。

看不惯论坛的也可以下源文件ourdev_613310QOJXK4.txt(文件大小:4K) (原文件名:代码.txt) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

该献的血还是要献的。你不献他不献。难道让我去献? --- 出自坛友:lovejp1981

|