|

|

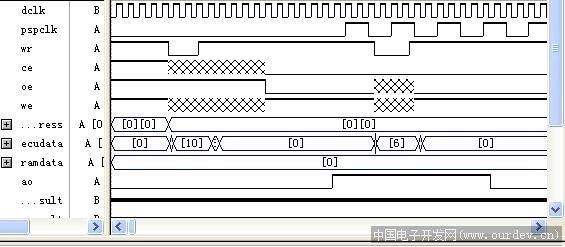

请各位帮看一下这段的VERILOG代码为啥,oe,ce,we 会变化时出现一段时间的XXXXXXXX

先谢过!

图:

(原文件名:1图.JPG)

程序段:

module vga(dclk,hs,vs,pspclk3,pspclk1,pspclk,ecudata,ao,wr,oe,ce,we,ramdata,ramaddress,hight);

input dclk,ao,wr;

input [7:0]ecudata;

output hs,vs,pspclk3,pspclk1,oe,ce,we,pspclk;

output [15:0]ramaddress;

output [3:0]hight;

inout [7:0]ramdata;

reg hs,vs,pspclk1,pspclk3,pspclk;

reg[10:0] count_v,count_h;

reg flag,j,start,nextstart;

reg [7:0]cmdreg;

reg [15:0]weARMADDR,rdARMADDR;

reg [7:0]ioreg,addl,addh,ramdata;

reg [3:0]hight1,low1,hight;

reg row,ce,oe,we;

wire si;

reg [21:0]sysen;

assign endata=(count_h>3&count_h<120)?1:0;

assign ramaddress=row?weARMADDR:rdARMADDR;

assign si=wr;

initial

begin

oe<=1;

ce<=1;

we<=1;

end

//always @(negedge wr)

//begin

// si<=1;

//end

always@ (posedge dclk or negedge si)//or negedge wr

begin

if(!si)

begin

case (start)

0:

begin

if(ao==1)//comm

cmdreg<=ecudata;

else//DATA

begin

if(cmdreg==8'h00)//written low 8bit address command

addl<=ecudata;

else if(cmdreg==8'h02)////written hight 8bit address command

begin

addh<=ecudata;

weARMADDR<={addh,addl};

end

else if(cmdreg==8'h04)//written data;

ioreg<=ecudata;

end

start<=1;

end

1:

begin

ce<=0;oe<=1;we<=0; //input ram

start<=2;row<=1;

end

2:

begin

if(weARMADDR==38399)

weARMADDR<=0;

start<=3;

end

3:

begin

ramdata<=ioreg;

weARMADDR<=weARMADDR+1;

start<=0;ce<=1;

end

endcase

end

else if(endata)

begin

case(nextstart)

0:begin

ce<=0;oe<=0;we<=1;row<=1;

nextstart<=1;

end

1:begin

hight1<=ramdata[7:4];low1<=ramdata[3:0];

nextstart<=2;

end

2:begin

if(rdARMADDR==38399)

rdARMADDR<=0;

rdARMADDR<=rdARMADDR+1;

nextstart<=3;

end

3:begin

ce<=1;hight<=hight1;

nextstart<=4;

end

4:begin

nextstart<=5;

end

5:begin

nextstart<=6;

end

6:begin

hight<=low1;

nextstart<=7;

end

7:begin

nextstart<=0;

ce<=1;

end

endcase

end

end |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|