|

|

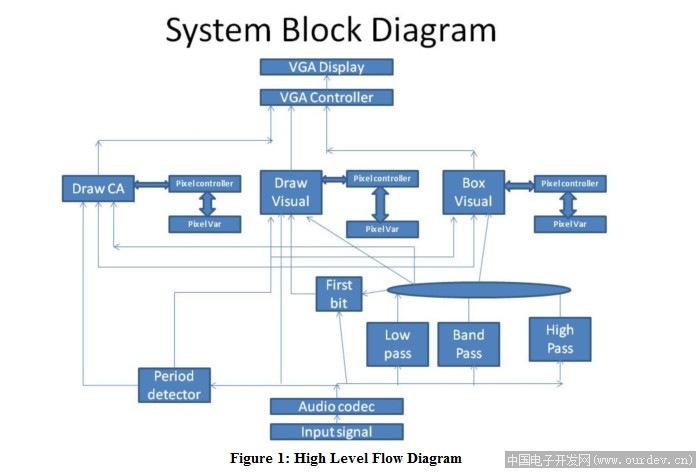

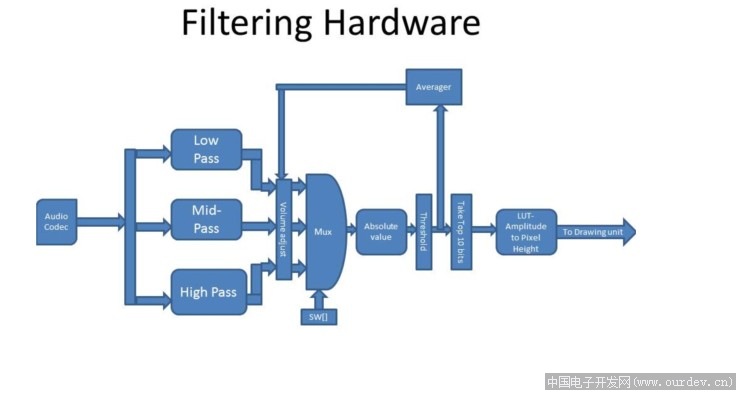

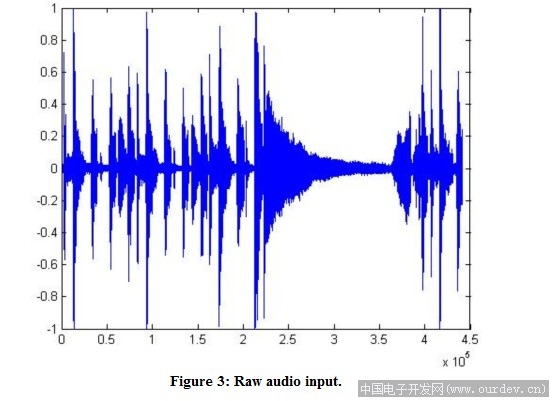

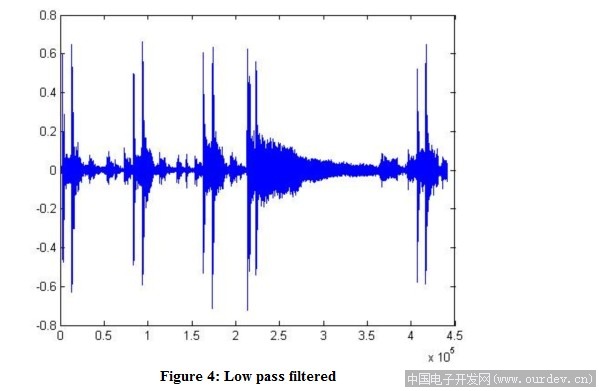

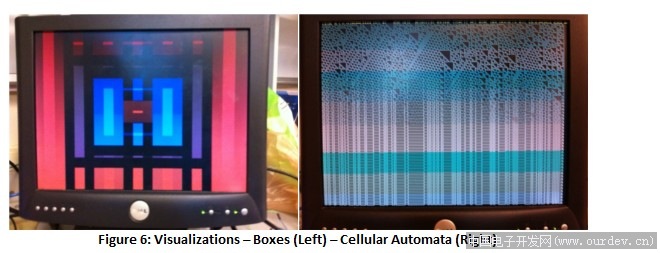

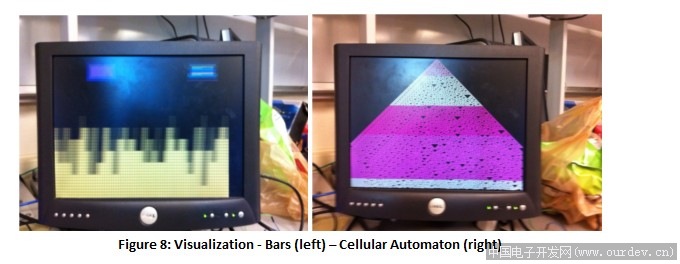

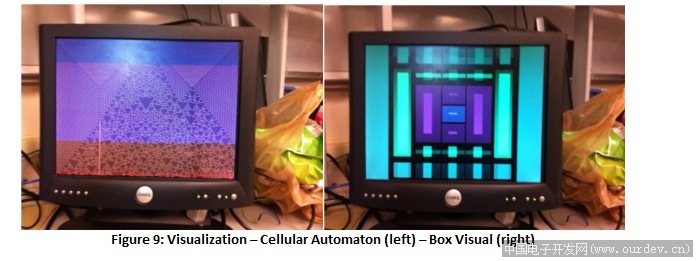

我们项目的目标是在输入信号的DE2开发板上,无论是音乐,谈话,或噪音,并能分析上显示的信号的实时VGA输出的视觉效果。主要的重点和完成这个项目的测试是通过对音乐的电脑上播放。该项目采用的是DE2开发板的设置,在船上的音频编解码器,以及与外部显示器的VGA显示驱动程序。安装程序将用户输入的线路板上,然后在他们的音乐我们的项目逻辑将在VGA端口输出的信号的视觉效果,根据未来英寸一旦信号进行分化的信号线路输入是必要的,做由振幅,频率和时间。使用不同的输入信号的可视化方案选择的用户显示这些不同的措施。该输入信号的幅度随着时间的推移转化为一个逻辑映射的VGA和VGA显示器上允许不同大小的物体。频率和周期是十分密切的关系进行了处理方式不同。我们使用的频率,以五过滤器分为三个波段的输入信号。乐队分别对应低音,钹,和人声和振幅和每个波段的显示板显示不同的图案和颜色相应的内容而定。最终的测量,周期,被用来在不同的方式为像素的VGA显示器上的颜色变化。根据多久时期是会改变颜色方案按照这个速度。颜色变化的像素也以更快的步伐进行,因此,如果检测到被占领的节拍季度票据步伐的颜色可以改变一个四分音符,二分音符,全音符,两个半笔记。每个音符的准确时间,并不一定准确,但是,相对起搏或每分钟心跳(BPM)的对音乐的目标。这个项目被选中的原因是因为音频可视化是共同找到,但不一定与正在播放的音乐。这个项目的目标是创建视觉效果,实际上遵循的一个更好的聆听体验音乐。

(原文件名:11.jpg)

(原文件名:22.jpg)

(原文件名:33.jpg)

(原文件名:44.jpg)

(原文件名:55.jpg)

(原文件名:66.jpg)

(原文件名:77.jpg)

(原文件名:88.jpg)

(原文件名:99.jpg)

(原文件名:100.jpg)

/////////////////////////////////////////////////////////////

///////// Audio Visualization ///////////////////////////////

//////// ECE 5760 - Final Project ///////////////////////////

//////// Michael Lyons - mpl56 //////////////////////////////

//////// Darbin Reyes - der34 ///////////////////////////////

/////////////////////////////////////////////////////////////

wire [31:0] mSEG7_DIG;

reg [31:0] Cont;

wire VGA_CTRL_CLK;

wire AUD_CTRL_CLK;

wire [9:0] mVGA_R;

wire [9:0] mVGA_G;

wire [9:0] mVGA_B;

wire [19:0] mVGA_ADDR; //video memory address

wire [9:0] Coord_X, Coord_Y; //display coods

wire DLY_RST;

assign TD_RESET = 1'b1; // Allow 27 MHz input

assign AUD_ADCLRCK = AUD_DACLRCK;

assign AUD_XCK = AUD_CTRL_CLK;

//modules needs for Audio codec and VGA

Reset_Delay r0 (.iCLK(CLOCK_50),.oRESET(DLY_RST) );

I2C_AV_Config u3 ( // Host Side

.iCLK(CLOCK_50),

.iRST_N(KEY[0]),

// I2C Side

.I2C_SCLK(I2C_SCLK),

.I2C_SDAT(I2C_SDAT) );

VGA_Audio_PLL p1 ( .areset(~DLY_RST),.inclk0(CLOCK_27),.c0(VGA_CTRL_CLK),.c1(AUD_CTRL_CLK),.c2(VGA_CLK) );

//////////////////////////////////////////////////////////

// output to audio DAC

wire signed [15:0] audio_outL, audio_outR ;

// input from audio ADC

wire signed [15:0] audio_inL, audio_inR ;

AUDIO_DAC_ADC u4 ( // Audio Side

.oAUD_BCK(AUD_BCLK),

.oAUD_DATA(AUD_DACDAT),

.oAUD_LRCK(AUD_DACLRCK),

.oAUD_inL(audio_inL), // audio data from ADC

.oAUD_inR(audio_inR), // audio data from ADC

.iAUD_ADCDAT(AUD_ADCDAT),

.iAUD_extL(audio_outL), // audio data to DAC

.iAUD_extR(audio_outR), // audio data to DAC

// Control Signals

.iCLK_18_4(AUD_CTRL_CLK),

.iRST_N(DLY_RST),

.isel(SW[17])

);

//////////////////////////////////////////////////////////

VGA_Controller u1 ( // Host Side

.iCursor_RGB_EN(4'b0111),

.oAddress(mVGA_ADDR),

.oCoord_X(Coord_X),

.oCoord_Y(Coord_Y),

.iRed(mVGA_R),

.iGreen(mVGA_G),

.iBlue(mVGA_B),

// VGA Side

.oVGA_R(VGA_R),

.oVGA_G(VGA_G),

.oVGA_B(VGA_B),

.oVGA_H_SYNC(VGA_HS),

.oVGA_V_SYNC(VGA_VS),

.oVGA_SYNC(VGA_SYNC),

.oVGA_BLANK(VGA_BLANK),

// Control Signal

.iCLK(VGA_CTRL_CLK),

.iRST_N(DLY_RST) );

// assign VGA outputs

assign mVGA_R = SW[1] ? {SRAM_DQ[14:10], 5'b0} : SW[0] ? barR : boxR;

assign mVGA_G = SW[1] ? {SRAM_DQ[9:5], 5'b0} : SW[0] ? barG : boxG;

assign mVGA_B = SW[1] ? {SRAM_DQ[4:0], 5'b0} : SW[0] ? barB : boxB;

///////////////////////////////////////////////////////////////

// SRAM_control

assign SRAM_ADDR = addr_reg;

assign SRAM_DQ = (we)? 16'hzzzz : data_reg ;

assign SRAM_UB_N = 0; // hi byte select enabled

assign SRAM_LB_N = 0; // lo byte select enabled

assign SRAM_CE_N = 0; // chip is enabled

assign SRAM_WE_N = we; // write when ZERO

assign SRAM_OE_N = 0; //output enable is overidden by WE

// reset wire

assign reset = ~KEY[0];

///////////////////////////////////////////////////////////////

//boxvisual instantiation /////////////////////////////////////

wire [9:0] boxR, boxG, boxB;

//module boxVisual(reset, CLK50, AUDCLK, VGA_VS, audIn, cymbal,bass,voice, coordX, coordY, period, red, green, blue);

boxVisual box1(reset, CLOCK_50, AUD_DACLRCK, VGA_VS, VGA_HS, audio_inL,IIR4outL_cymbal2,IIR4outL_bass2,IIR4outL_voice2,Coord_X[9:1],Coord_Y[9:1],maxPerLength,boxR,boxG,boxB);

////////////////////////////////////

// bar pixel values

wire [9:0] barR, barG, barB;

//module drawBars(iHeight,iX,iY,iVGA_VS,iVGA_HS,oR,oG,oB,CLK,VGACLK,AUDCLK,CLK27,audIn,RST,state,period);

//module drawBars(iHeight,iX,iY,iVGA_VS,iVGA_HS,oR,oG,oB,CLK,VGACLK,AUDCLK,CLK27,audIn,RST,state,period,bassH,cymbalH,voiceH,sigSel);

drawBars uBars(.iHeight(hbitamp), //draw bars

.iX(Coord_X),

.iY(Coord_Y),

.iVGA_VS(VGA_VS),

.iVGA_HS(VGA_HS),

.oR(barR),

.oG(barG),

.oB(barB),

.CLK(CLOCK_50),

.VGACLK(VGA_CTRL_CLK),

.AUDCLK(AUD_DACLRCK),

.CLK27(CLOCK_27),

.audIn(audio_inL),

.bass(IIR4outL_bass2),

.cymbal(IIR4outL_cymbal2),

.voice(IIR4outL_voice2),

.RST(~KEY[0]),

.state(blank),

.period(maxPerLength),

.bassH(bassHbit),

.cymbalH(cymbalHbit),

.voiceH(voiceHbit),

.sigSel(SW[10:6])

);

////////////////////////////////////////////////

///////////// CA visualization /////////////////

////////////////////////////////////////////////

//////////////////////////////////////////////////////////////////////

//most important vars to know about

wire reset;

reg [17:0] addr_reg; //memory address register for SRAM

reg [15:0] data_reg; //memory data register for SRAM

reg we ; //write enable for SRAM

reg [3:0] state; //state machine

reg lock; //did we stay in sync?

reg [7:0] rule; // to store the CA rule

reg randinit; //signal to init the first line to random black/white

reg [30:0] x_rand; //shift registers for random number gen

wire x_low_bit; //rand low bits for SR

reg [8:0] x_walker; //current position coords

reg [8:0] y_walker;

reg [2:0] sum; //neighbors state

///////////////////////////////////////////////////////////////////////

//right-most bit for rand number shift regs

//your basic XOR random # gen

assign x_low_bit = x_rand[27] ^ x_rand[30];

/// pixel controller logic

wire [9:0] CAR, CAG, CAB;

//module pixelController(reset, schemeReset, CLK, CLK27, AUDCLK, VGA_VS, VGA_HS, audIn, periodIn, red, green, blue);

pixelController unit1(reset, 8'd16, CLOCK_50, CLOCK_27, AUDCLK, VGA_VS, VGA_HS, audio_inL, (maxPerLength>>4), CAR, CAG, CAB);

//state names for machines that draws automata

parameter test1=4'd1, test2=4'd2, test3=4'd3, test4=4'd4,

draw_walker=4'd5, update_walker=4'd6, user_wait=4'd7;

//state names for machine tha copies bottom line to top line

parameter cinit=4'd0, cread=4'd1,csave=4'd2, cwrite=4'd3;

reg [31:0] countCA;

reg rand;

reg [4:0] bassColor, cymbalColor, voiceColor;

reg [14:0] bassFull, cymbalFull, voiceFull, audioFull;

// on VGA control clock run CA

always @ (posedge VGA_CTRL_CLK) begin

bassColor <= IIR4outL_bass2[15:11];

cymbalColor <= IIR4outL_cymbal2[15:11];

voiceColor <= IIR4outL_voice2[15:11];

bassFull <= IIR4outL_bass2[14:0];

cymbalFull <= IIR4outL_cymbal2[14:0];

voiceFull <= IIR4outL_voice2[14:0];

audioFull <= audio_inL[14:0];

if (reset) begin //synch reset assumes KEY0 is held down 1/60 second

//clear the screen

addr_reg <= {Coord_X[9:1],Coord_Y[9:1]} ; // [17:0]

we <= 1'b0; //write some memory

data_reg <= 16'b0; //write all zeros (black)

rand <= 1'd0;

if(rand)begin //init top line of screen to random black white

x_walker <= 9'd0; //start at 0,0 to make sure every pixel is assign a random color

y_walker <= 9'd0;

randinit <=1'b1;

end else begin

x_walker <= 9'd1; //otherwise start one pixexl to the right to force a black border

y_walker <= 9'd0;

randinit <=1'b1;

x_rand <= 31'h55555555;//init random number generator to alternating bits

end

//get rule from switches

rule <= 8'd1;//SW[7:0];

state <= test1; //first state in drawing state machine

end

else if(randinit) begin// assign the top line random colors if SW17 is high, else single dot at top center

if(rand) begin//random colors

if(x_walker <=9'd319) begin//entire line

x_rand <= {x_rand[29:0], x_low_bit} ; //update the x,y random number gens

addr_reg <= {x_walker,y_walker}; //write to the pixels on the top line

we <= 1'b0; //write

if(x_rand[30]) data_reg <= SW[3] ? {1'b1,bassColor,cymbalColor,voiceColor} : {1'b1,CAR[9:5],CAG[9:5],CAB[9:5]} ; //white pixel

else data_reg <= 16'b0; //black pixel

x_walker <= x_walker+9'd1; //next pixel

end else begin

x_walker <= 9'd1;

y_walker <= 9'd0;

we <= 1'b1; //stop writing to mem

randinit<= 1'b0; //done drawing random line

end

end else begin//single dot at top center

addr_reg <= {9'd160,9'd0} ; //init to single dot

//write a white dot in the middle of the screen

we <= 1'b0;

data_reg <= {1'b1, CAR[9:5],CAG[9:5],CAB[9:5]} ;

randinit<= 1'b0;

end

end else if ((~VGA_VS | ~VGA_HS)) begin //sync is active low //modify display during sync*/

case(state)

test1: begin//read self

we <= 1'b1; //no memory write

lock <= 1'b1; //set the interlock to detect end of sync interval

sum <= 3'b0; //init neighbor state

addr_reg <= {x_walker,y_walker};//read self

state <= test2 ;

end

test2: begin//check self and read left neighbor

if(lock) begin//must check lock before reading to make sure the right value is read

we <= 1'b1; //no memory write

sum[1] <=SRAM_DQ[15];

//read left neighbor

addr_reg <= {x_walker-9'd1,y_walker};

state <= test3 ;

end else state <= test1 ; //otherwise start over because addr_reg was destroyed by VGA controller

end

test3: begin//check left neighbor and read right neighbor

if(lock)begin

we <= 1'b1; //no memory write

sum[2] <=SRAM_DQ[15];

//read right neighbor

addr_reg <= {x_walker+ 9'd1,y_walker };

state <= test4 ;

end else state <= test1 ;

end

test4: begin//check right neighbor

if(lock)begin

we <= 1'b1; //no memory write

sum[0] <=SRAM_DQ[15];

state <= draw_walker ;

end else state <= test1 ;

end

draw_walker: begin//light up cell in next generation

if(lock) begin// if we got this far, then the sum var it correct so spin on the lock until you get a chance to write

we <= 1'b0; // memory write

addr_reg <= {x_walker,y_walker+1'b1}; //cell below this one

if(rule[sum])begin

case(SW[5:3])

3'd0: data_reg <= {1'b1,bassColor,cymbalColor,voiceColor};

3'd1: data_reg <= {1'b1,bassFull};

3'd2: data_reg <= {1'b1,cymbalFull};

3'd3: data_reg <= {1'b1,voiceFull};

3'd4: data_reg <= {1'b1,audioFull};

default: data_reg <= {1'b1,CAR[9:5],CAG[9:5],CAB[9:5]} ; //pixel variator unit

endcase

end else begin

data_reg <= 16'b0 ; //black

end

state <= update_walker ; //move to next cell

end else begin

state <= draw_walker;

lock <= 1'b1; //set the interlock to detect end of sync interval

end

end

update_walker: begin//update the walker

we <= 1'b1; //no mem write

//move to next pixel

if (x_walker<9'd318 & y_walker < 9'd237)begin

x_walker <= x_walker+9'd1;

state <= test1 ;

end else if (x_walker == 9'd318 & y_walker < 9'd237)begin

x_walker <= 9'd1;

y_walker <= y_walker+9'd1;

state <= test1 ;

end else begin

state <= user_wait;//test1 ; //done, just loop

end

end

user_wait: begin//wait for user to do something

if (SW[1]&SW[12]) begin

countCA <= countCA + 32'd1;

if (countCA > (maxPerLength)) begin

countCA <= 32'd0;

if (SW[2]) begin

rule <= rule + 8'd1;

end else begin

rule <= maxPerLength[20:13];

end

if (rule==8'd255) begin

if (SW[2]) rule <= 8'd1;

else rule <= maxPerLength[20:13];

rand <= ~rand;

end

x_walker <= 0;

y_walker <= 0;

if(rand) randinit <= 1'd1;

state <= test1;

end

end else begin

//randinit <= SW[4];

state <= user_wait;

end

end

endcase

end else begin

//show display when not blanking, which implies we=1 (not enabled); and use VGA module address

lock <= 1'b0; //clear lock if display starts because this destroys mem addr_reg

addr_reg <= {Coord_X[9:1],Coord_Y[9:1]} ;

we <= 1'b1;

end

end

// assign the current rule to the green LEDs

assign LEDG = rule;

assign LEDR = SRAM_DQ;

//////////////////////////////////////////////

//Period calculation that needs to be done in top module

//parameters

parameter firstCross = 3'd0, secondCross = 3'd1, thirdCross = 3'd2;

parameter firstSample = 3'd3, secondSample = 3'd4, thirdSample = 3'd5;

//registers

reg clk1000;

reg [2:0] state1000;

reg [9:0] newMax;

reg signed [15:0] sample1000, prevSample, hzCount;

reg [31:0] periodCount, periodLength, maxPerLength;

reg signed [15:0] modIn;

//wires

//wire signed [15:0] CIC_out1;

wire signed [15:0] oCIC;

//wire signed [15:0] temp;

//outputs

reg [31:0] period;

// down sample to audio rate

CIC_N2_M1_16bit_fixed f1(oCIC, modIn, CLOCK_27, AUD_DACLRCK, reset);

// sample audio in at 27 MHz

always @ (posedge CLOCK_27) begin

modIn <= audio_inL;

end

// period calculation via zero crossing

always @ (posedge CLOCK_50) begin

// bass beat finding

periodCount <= periodCount + 32'd1;

hzCount <= hzCount + 16'd1;

// create a 1000 Hz signal to alias all high freqencies to get

// accurate measurements on the lowest frequencies

if (hzCount>16'd25000) begin

hzCount <= 16'd0;

if (clk1000) begin

clk1000 <= 1'd0;

end else begin

clk1000 <= 1'd1;

end

end

//if reset then set all registers to zero

if (reset) begin

maxPerLength <= 0;

prevSample <= 0;

newMax <= 0;

state1000 <= firstSample;

end else begin

case(state1000)

// on high 1000 Hz take sample of CIC filter output

firstSample: begin

if (clk1000) begin

sample1000 <= oCIC;//CIC_out1;

state1000 <= firstCross;

end

end

// wait for a sign change in the CIC output

firstCross: begin

// if there is a change from positive to negative go to next sample

if((prevSample>0)&&(0>sample1000))begin

periodCount <= 32'd0;

prevSample <= sample1000;

state1000 <= secondSample;

// if there is a change from negative to positive go to next sample

end else if ((prevSample<0)&&(0<sample1000))begin

periodCount <= 32'd0;

prevSample <= sample1000;

state1000 <= secondSample;

end else begin // no change get a new sample

prevSample <= sample1000;

state1000 <= firstSample;

end

end

// on high 1000 Hz take sample of CIC filter output

secondSample: begin

if (clk1000) begin

sample1000 <= oCIC;//CIC_out1;

state1000 <= secondCross;

end

end

// wait for a sign change in the CIC output

// second cross for mid way through waveform

secondCross: begin

// if there is a change from positive to negative go to next sample

if((prevSample>0)&&(0>sample1000))begin

prevSample <= sample1000;

state1000 <= thirdSample;

// if there is a change from negative to positive go to next sample

end else if ((prevSample<0)&&(0<sample1000))begin

prevSample <= sample1000;

state1000 <= thirdSample;

end else begin // no change get a new sample

prevSample <= sample1000;

state1000 <= secondSample;

end

end

// on high 1000 Hz take sample of CIC filter output

thirdSample: begin

if (clk1000) begin

sample1000 <= oCIC;//CIC_out1;

state1000 <= thirdCross;

end

end

// wait for a sign change in the CIC output

// third cross for full period measurement

thirdCross: begin

// if there is a change from positive to negative go to next sample

if((prevSample>0)&&(0>sample1000))begin

periodLength <= periodCount;

newMax <= newMax + 10'd1;

if(newMax > 10'd1000)begin // get a new max period length

newMax <= 10'd0;

maxPerLength <= 32'd1000;

end else if(periodLength > maxPerLength) begin // if new period is larger save it

maxPerLength <= periodLength;

end

prevSample <= sample1000;

state1000 <= firstSample;

// if there is a change from negative to positive go to next sample

end else if ((prevSample<0)&&(0<sample1000))begin

periodLength <= periodCount;

newMax <= newMax + 10'd1;

if(newMax > 10'd1000)begin // get a new max period length

newMax <= 10'd0;

maxPerLength <= 32'd1000;

end else if(periodLength > maxPerLength) begin// if new period is larger save it

maxPerLength <= periodLength;

end

prevSample <= sample1000;

state1000 <= firstSample;

end else begin // no change get a new sample

prevSample <= sample1000;

state1000 <= thirdSample;

end

end

endcase

end//

end// end always

// assign which signal you want to output

reg [15:0] audOut;

always @ (posedge CLOCK_50) begin

case(SW[16:14])

3'd0: begin

audOut <= oCIC; // output the CIC filter

end

3'd1: begin

audOut <= audio_inL; // normal audio input

end

3'd2: begin

audOut <= IIR4outL_cymbal2; // cymbal filter output

end

3'd3: begin

audOut <= IIR4outL_bass2; // bass filter output

end

3'd4: begin

audOut <= IIR4outL_voice2; // voice filter output

end

3'd5: begin

audOut <= sample1000;

end

default audOut <= 16'd0;

endcase

end

// audio outputs assign to wires

assign audio_outL = audOut;//CIC_out1;

assign audio_outR = audOut;

// max period length calculation counter displayed on red LEDs

//assign LEDR = newMax;

///////////////////////////////////////////////////////////////////

/////////////////// absolute value unit ///////////////////////////

///////////////////////////////////////////////////////////////////

wire signed [15:0] absoutL; // output of abs unit

wire signed [15:0] absBass, absCymbal, absVoice;

abs uabsL(absoutL, audio_outR, 4'd0,AUD_DACLRCK); //takes absolute value of input

abs absbass(absBass, IIR4outL_bass2, 4'd0,AUD_DACLRCK);

abs abscymbal(absCymbal, IIR4outL_cymbal2, 4'd0,AUD_DACLRCK);

abs absvoice(absVoice, IIR4outL_voice2, 4'd0,AUD_DACLRCK);

///////////////////////////////////////////////////////////////////

////////////////////// find the highest order bit /////////////////

///////////////////////////////////////////////////////////////////

// highest order bit output

wire [9:0] hbitamp, bassHbit, cymbalHbit, voiceHbit;

firstHbit hb(absoutL[15:6],hbitamp,CLOCK_50); //bit quatize bar height

firstHbit hbbass(absBass[15:6],bassHbit,CLOCK_50); //bit quatize bar height

firstHbit hbcymbal(absCymbal[15:6],cymbalHbit,CLOCK_50); //bit quatize bar height

firstHbit hbvoice(absVoice[15:6],voiceHbit,CLOCK_50); //bit quatize bar height

///////////////////////////////////////////////////////////////////

/////////////////////// 7 segment displays ////////////////////////

///////////////////////////////////////////////////////////////////

HexDigit h0(HEX0, maxPerLength[3:0]);

HexDigit h1(HEX1, maxPerLength[7:4]);

HexDigit h2(HEX2, maxPerLength[11:8]);

HexDigit h3(HEX3, maxPerLength[15:12]);

HexDigit h4(HEX4, maxPerLength[19:16]);

HexDigit h5(HEX5, maxPerLength[23:20]);

HexDigit h6(HEX6, maxPerLength[27:24]);

HexDigit h7(HEX7, maxPerLength[31:28]);

///////////////////////// Filter outputs declared /////////////////

wire signed [15:0] IIR4outL_voice1,IIR4outL_voice2;

wire signed [15:0] IIR4outL_cymbal1,IIR4outL_cymbal2;

wire signed [15:0] IIR4outL_bass1,IIR4outL_bass2;

///////////////////////////////////////////////////////////////////

/////////////////////// cymbal filtering //////////////////////////

/////////////////Filter: cutoff=0.5 ,cheby1 high //////////////////

///////////////////////////////////////////////////////////////////

IIR4_18bit_fixed IIR4L_cymb1(

.audio_out (IIR4outL_cymbal1),

.audio_in (audio_inL),

.scale (3'd1),

.b1 (18'hCA7),

.b2 (18'h3CD63),

.b3 (18'h4BEC),

.b4 (18'h3CD63),

.b5 (18'hCA7),

.a2 (18'h3FC41),

.a3 (18'h3A7AA),

.a4 (18'h3EE8D),

.a5 (18'h3F654),

.state_clk(AUD_CTRL_CLK),

.lr_clk(AUD_DACLRCK),

.reset(reset)

) ; //end filter

///////////////////////////////////////////////////////////////////

//////////////// Filter: cutoff=0.6 ,cheby1 low ///////////////////

///////////////////////////////////////////////////////////////////

IIR4_18bit_fixed IIR4L_cymb2(

.audio_out (IIR4outL_cymbal2),

.audio_in (IIR4outL_cymbal1),

.scale (3'd1),

.b1 (18'h1682),

.b2 (18'h5A0A),

.b3 (18'h8710),

.b4 (18'h5A0A),

.b5 (18'h1682),

.a2 (18'h398AF),

.a3 (18'h395A5),

.a4 (18'h3EE6B),

.a5 (18'h3F6EC),

.state_clk(AUD_CTRL_CLK),

.lr_clk(AUD_DACLRCK),

.reset(reset)

) ; //end filter

///////////////////////////////////////////////////////////////////

/////////////////bass beat filter//////////////////////////////////

///////// Filter: cutoff=0.02 , cheby1 low ////////////////////////

///////////////////////////////////////////////////////////////////

IIR4_27bit IIR4_bass1(

.audio_out (IIR4outL_bass2),

.audio_in (audio_inL),

.scale (3'd2),

.b1 (27'hF),

.b2 (27'h3E),

.b3 (27'h5D),

.b4 (27'h3E),

.b5 (27'hF),

.a2 (27'hF492E6),

.a3 (27'h6A0C0AB),

.a4 (27'hE0AA7A),

.a5 (27'h7CA00F9),

.state_clk(AUD_CTRL_CLK),

.lr_clk(AUD_DACLRCK),

.reset(reset)

) ; //end filter

///////////////////////////////////////////////////////////////////

//////////////////////////guitar/voice filter//////////////////////

////////////////// Filter: cutoff=0.05 ,cheby1 high ///////////////

///////////////////////////////////////////////////////////////////

IIR4_27bit IIR4_voice1(

.audio_out (IIR4outL_voice1),

.audio_in (audio_inL),

.scale (3'd2),

.b1 (27'h3426B9),

.b2 (27'h72F651C),

.b3 (27'h138E856),

.b4 (27'h72F651C),

.b5 (27'h3426B9),

.a2 (27'hE7331D),

.a3 (27'h6C586C9),

.a4 (27'hBED26A),

.a5 (27'h7D469AF),

.state_clk(AUD_CTRL_CLK),

.lr_clk(AUD_DACLRCK),

.reset(reset)

) ; //end filter

///////////////////////////////////////////////////////////////////

/////////////// Filter: cutoff=0.06 ,cheby1 low ///////////////////

///////////////////////////////////////////////////////////////////

IIR4_27bit IIR4_voice2(

.audio_out (IIR4outL_voice2),

.audio_in (IIR4outL_voice1),

.scale (3'd2),

.b1 (27'hE5),

.b2 (27'h395),

.b3 (27'h560),

.b4 (27'h395),

.b5 (27'hE5),

.a2 (27'hE8252D),

.a3 (27'h6C15AFD),

.a4 (27'hC401F3),

.a5 (27'h7D26F62),

.state_clk(AUD_CTRL_CLK),

.lr_clk(AUD_DACLRCK),

.reset(reset)

) ; //end filter

///////////////////////////////////////////////////////////////////

endmodule //top module

///////////////////////////////////////////////////////////////////

//////////////////// draw bars visualization //////////////////////

////////////////////////////////////draw bars//////////////////////

module drawBars(iHeight,iX,iY,iVGA_VS,iVGA_HS,oR,oG,oB,CLK,VGACLK,AUDCLK,CLK27,audIn,bass,cymbal,voice,RST,state,period,bassH,cymbalH,voiceH,sigSel);

// parameters

parameter init=4'd0, color=4'd1,eyeheight=10'd20,eyewidth=10'd60;

// inputs

input [4:0] sigSel;

input [9:0] iHeight, bassH, cymbalH, voiceH; //height of bar

input [9:0] iY; //VGA coordinates

input [9:0] iX;

input [31:0] period;

input [15:0] audIn, bass, cymbal,voice;

input CLK,RST,VGACLK, AUDCLK, CLK27;

input iVGA_VS,iVGA_HS; //vga sync

//outputs

output [3:0] state;

output [9:0] oR,oG,oB; //vga colors

//wires

wire eye1,eye2;

wire [9:0] red, green, blue;

// all column wires declared

wire c0,c1,c2,c3,c4,c5,c6,c7,c8,c9,c10,c11,c12,c13,c14,c15,c16,c17,c18,c19,c20,c21,c22,c23,c24,c25,c26,c27,c28,c29,c30,c31,c32,c33,c34,c35,c36,c37,c38,c39,c40,c41,c42,c43,c44,c45,c46,c47,c48,c49,c50,c51,c52,c53,c54,c55,c56,c57,c58,c59,c60,c61,c62,c63,c64,c65,c66,c67,c68,c69,c70,c71,c72,c73,c74,c75,c76,c77,c78,c79,c80,c81,c82,c83,c84,c85,c86,c87,c88,c89,c90,c91,c92,c93,c94,c95,c96,c97,c98,c99;

//registers

reg [9:0] reg_R,reg_G,reg_B,x,y;

reg [15:0] sampleAudio, sampleBass, sampleCymbal, sampleVoice;

reg switchColor;

reg [23:0] sampleCount;

reg [3:0] draw_state;

reg [9:0] redValue, greenValue, blueValue;

// all heights registers declared

reg [9:0] height_reg0;

reg [9:0] height_reg1;

reg [9:0] height_reg2;

reg [9:0] height_reg3;

reg [9:0] height_reg4;

reg [9:0] height_reg5;

reg [9:0] height_reg6;

reg [9:0] height_reg7;

reg [9:0] height_reg8;

reg [9:0] height_reg9;

reg [9:0] height_reg10;

reg [9:0] height_reg11;

reg [9:0] height_reg12;

reg [9:0] height_reg13;

reg [9:0] height_reg14;

reg [9:0] height_reg15;

reg [9:0] height_reg16;

reg [9:0] height_reg17;

reg [9:0] height_reg18;

reg [9:0] height_reg19;

reg [9:0] height_reg20;

reg [9:0] height_reg21;

reg [9:0] height_reg22;

reg [9:0] height_reg23;

reg [9:0] height_reg24;

reg [9:0] height_reg25;

reg [9:0] height_reg26;

reg [9:0] height_reg27;

reg [9:0] height_reg28;

reg [9:0] height_reg29;

reg [9:0] height_reg30;

reg [9:0] height_reg31;

reg [9:0] height_reg32;

reg [9:0] height_reg33;

reg [9:0] height_reg34;

reg [9:0] height_reg35;

reg [9:0] height_reg36;

reg [9:0] height_reg37;

reg [9:0] height_reg38;

reg [9:0] height_reg39;

reg [9:0] height_reg40;

reg [9:0] height_reg41;

reg [9:0] height_reg42;

reg [9:0] height_reg43;

reg [9:0] height_reg44;

reg [9:0] height_reg45;

reg [9:0] height_reg46;

reg [9:0] height_reg47;

reg [9:0] height_reg48;

reg [9:0] height_reg49;

reg [9:0] height_reg50;

reg [9:0] height_reg51;

reg [9:0] height_reg52;

reg [9:0] height_reg53;

reg [9:0] height_reg54;

reg [9:0] height_reg55;

reg [9:0] height_reg56;

reg [9:0] height_reg57;

reg [9:0] height_reg58;

reg [9:0] height_reg59;

reg [9:0] height_reg60;

reg [9:0] height_reg61;

reg [9:0] height_reg62;

reg [9:0] height_reg63;

reg [9:0] height_reg64;

reg [9:0] height_reg65;

reg [9:0] height_reg66;

reg [9:0] height_reg67;

reg [9:0] height_reg68;

reg [9:0] height_reg69;

reg [9:0] height_reg70;

reg [9:0] height_reg71;

reg [9:0] height_reg72;

reg [9:0] height_reg73;

reg [9:0] height_reg74;

reg [9:0] height_reg75;

reg [9:0] height_reg76;

reg [9:0] height_reg77;

reg [9:0] height_reg78;

reg [9:0] height_reg79;

reg [9:0] height_reg80;

reg [9:0] height_reg81;

reg [9:0] height_reg82;

reg [9:0] height_reg83;

reg [9:0] height_reg84;

reg [9:0] height_reg85;

reg [9:0] height_reg86;

reg [9:0] height_reg87;

reg [9:0] height_reg88;

reg [9:0] height_reg89;

reg [9:0] height_reg90;

reg [9:0] height_reg91;

reg [9:0] height_reg92;

reg [9:0] height_reg93;

reg [9:0] height_reg94;

reg [9:0] height_reg95;

reg [9:0] height_reg96;

reg [9:0] height_reg97;

reg [9:0] height_reg98;

reg [9:0] height_reg99;

//pixelVar unit1(reset, iVGA_VS, CLK, switch[10:8], switch[7], switch[6:5], switch[4:3], switch[2], switch[1], switch[0], red, green, blue);

//pixelController(reset, CLK, CLK27, AUDCLK, VGA_VS, audIn, periodIn, red, green, blue);

pixelController unit1(reset, 8'd16, CLK, CLK27, AUDCLK, iVGA_VS, iVGA_HS, audIn, period, red, green, blue);

// all column values

assign c0=iY > height_reg0 & iX>10'd0 & iX<10'd6;

assign c1=iY > height_reg1 & iX>10'd6 & iX<10'd12;

assign c2=iY > height_reg2 & iX>10'd12 & iX<10'd18;

assign c3=iY > height_reg3 & iX>10'd18 & iX<10'd24;

assign c4=iY > height_reg4 & iX>10'd24 & iX<10'd30;

assign c5=iY > height_reg5 & iX>10'd30 & iX<10'd36;

assign c6=iY > height_reg6 & iX>10'd36 & iX<10'd42;

assign c7=iY > height_reg7 & iX>10'd42 & iX<10'd48;

assign c8=iY > height_reg8 & iX>10'd48 & iX<10'd54;

assign c9=iY > height_reg9 & iX>10'd54 & iX<10'd60;

assign c10=iY > height_reg10 & iX>10'd60 & iX<10'd66;

assign c11=iY > height_reg11 & iX>10'd66 & iX<10'd72;

assign c12=iY > height_reg12 & iX>10'd72 & iX<10'd78;

assign c13=iY > height_reg13 & iX>10'd78 & iX<10'd84;

assign c14=iY > height_reg14 & iX>10'd84 & iX<10'd90;

assign c15=iY > height_reg15 & iX>10'd90 & iX<10'd96;

assign c16=iY > height_reg16 & iX>10'd96 & iX<10'd102;

assign c17=iY > height_reg17 & iX>10'd102 & iX<10'd108;

assign c18=iY > height_reg18 & iX>10'd108 & iX<10'd114;

assign c19=iY > height_reg19 & iX>10'd114 & iX<10'd120;

assign c20=iY > height_reg20 & iX>10'd120 & iX<10'd126;

assign c21=iY > height_reg21 & iX>10'd126 & iX<10'd132;

assign c22=iY > height_reg22 & iX>10'd132 & iX<10'd138;

assign c23=iY > height_reg23 & iX>10'd138 & iX<10'd144;

assign c24=iY > height_reg24 & iX>10'd144 & iX<10'd150;

assign c25=iY > height_reg25 & iX>10'd150 & iX<10'd156;

assign c26=iY > height_reg26 & iX>10'd156 & iX<10'd162;

assign c27=iY > height_reg27 & iX>10'd162 & iX<10'd168;

assign c28=iY > height_reg28 & iX>10'd168 & iX<10'd174;

assign c29=iY > height_reg29 & iX>10'd174 & iX<10'd180;

assign c30=iY > height_reg30 & iX>10'd180 & iX<10'd186;

assign c31=iY > height_reg31 & iX>10'd186 & iX<10'd192;

assign c32=iY > height_reg32 & iX>10'd192 & iX<10'd198;

assign c33=iY > height_reg33 & iX>10'd198 & iX<10'd204;

assign c34=iY > height_reg34 & iX>10'd204 & iX<10'd210;

assign c35=iY > height_reg35 & iX>10'd210 & iX<10'd216;

assign c36=iY > height_reg36 & iX>10'd216 & iX<10'd222;

assign c37=iY > height_reg37 & iX>10'd222 & iX<10'd228;

assign c38=iY > height_reg38 & iX>10'd228 & iX<10'd234;

assign c39=iY > height_reg39 & iX>10'd234 & iX<10'd240;

assign c40=iY > height_reg40 & iX>10'd240 & iX<10'd246;

assign c41=iY > height_reg41 & iX>10'd246 & iX<10'd252;

assign c42=iY > height_reg42 & iX>10'd252 & iX<10'd258;

assign c43=iY > height_reg43 & iX>10'd258 & iX<10'd264;

assign c44=iY > height_reg44 & iX>10'd264 & iX<10'd270;

assign c45=iY > height_reg45 & iX>10'd270 & iX<10'd276;

assign c46=iY > height_reg46 & iX>10'd276 & iX<10'd282;

assign c47=iY > height_reg47 & iX>10'd282 & iX<10'd288;

assign c48=iY > height_reg48 & iX>10'd288 & iX<10'd294;

assign c49=iY > height_reg49 & iX>10'd294 & iX<10'd300;

assign c50=iY > height_reg50 & iX>10'd300 & iX<10'd306;

assign c51=iY > height_reg51 & iX>10'd306 & iX<10'd312;

assign c52=iY > height_reg52 & iX>10'd312 & iX<10'd318;

assign c53=iY > height_reg53 & iX>10'd318 & iX<10'd324;

assign c54=iY > height_reg54 & iX>10'd324 & iX<10'd330;

assign c55=iY > height_reg55 & iX>10'd330 & iX<10'd336;

assign c56=iY > height_reg56 & iX>10'd336 & iX<10'd342;

assign c57=iY > height_reg57 & iX>10'd342 & iX<10'd348;

assign c58=iY > height_reg58 & iX>10'd348 & iX<10'd354;

assign c59=iY > height_reg59 & iX>10'd354 & iX<10'd360;

assign c60=iY > height_reg60 & iX>10'd360 & iX<10'd366;

assign c61=iY > height_reg61 & iX>10'd366 & iX<10'd372;

assign c62=iY > height_reg62 & iX>10'd372 & iX<10'd378;

assign c63=iY > height_reg63 & iX>10'd378 & iX<10'd384;

assign c64=iY > height_reg64 & iX>10'd384 & iX<10'd390;

assign c65=iY > height_reg65 & iX>10'd390 & iX<10'd396;

assign c66=iY > height_reg66 & iX>10'd396 & iX<10'd402;

assign c67=iY > height_reg67 & iX>10'd402 & iX<10'd408;

assign c68=iY > height_reg68 & iX>10'd408 & iX<10'd414;

assign c69=iY > height_reg69 & iX>10'd414 & iX<10'd420;

assign c70=iY > height_reg70 & iX>10'd420 & iX<10'd426;

assign c71=iY > height_reg71 & iX>10'd426 & iX<10'd432;

assign c72=iY > height_reg72 & iX>10'd432 & iX<10'd438;

assign c73=iY > height_reg73 & iX>10'd438 & iX<10'd444;

assign c74=iY > height_reg74 & iX>10'd444 & iX<10'd450;

assign c75=iY > height_reg75 & iX>10'd450 & iX<10'd456;

assign c76=iY > height_reg76 & iX>10'd456 & iX<10'd462;

assign c77=iY > height_reg77 & iX>10'd462 & iX<10'd468;

assign c78=iY > height_reg78 & iX>10'd468 & iX<10'd474;

assign c79=iY > height_reg79 & iX>10'd474 & iX<10'd480;

assign c80=iY > height_reg80 & iX>10'd480 & iX<10'd486;

assign c81=iY > height_reg81 & iX>10'd486 & iX<10'd492;

assign c82=iY > height_reg82 & iX>10'd492 & iX<10'd498;

assign c83=iY > height_reg83 & iX>10'd498 & iX<10'd504;

assign c84=iY > height_reg84 & iX>10'd504 & iX<10'd510;

assign c85=iY > height_reg85 & iX>10'd510 & iX<10'd516;

assign c86=iY > height_reg86 & iX>10'd516 & iX<10'd522;

assign c87=iY > height_reg87 & iX>10'd522 & iX<10'd528;

assign c88=iY > height_reg88 & iX>10'd528 & iX<10'd534;

assign c89=iY > height_reg89 & iX>10'd534 & iX<10'd540;

assign c90=iY > height_reg90 & iX>10'd540 & iX<10'd546;

assign c91=iY > height_reg91 & iX>10'd546 & iX<10'd552;

assign c92=iY > height_reg92 & iX>10'd552 & iX<10'd558;

assign c93=iY > height_reg93 & iX>10'd558 & iX<10'd564;

assign c94=iY > height_reg94 & iX>10'd564 & iX<10'd570;

assign c95=iY > height_reg95 & iX>10'd570 & iX<10'd576;

assign c96=iY > height_reg96 & iX>10'd576 & iX<10'd582;

assign c97=iY > height_reg97 & iX>10'd582 & iX<10'd588;

assign c98=iY > height_reg98 & iX>10'd588 & iX<10'd594;

assign c99=iY > height_reg99 & iX>10'd594 & iX<10'd600;

//eye tracking

assign eye1= iY >10'd40-height_reg10[4:0] & iY <10'd40+eyeheight+height_reg10[4:0] & iX >10'd140-height_reg10[4:0] & iX <10'd140+eyewidth+height_reg10[4:0];

assign eye2= iY >10'd40-height_reg20[4:0] & iY <10'd40+eyeheight+height_reg20[4:0] & iX >10'd480-height_reg20[4:0] & iX <10'd480+eyewidth+height_reg20[4:0];

always @ (posedge CLK) begin

if(RST) begin //reset

switchColor<=0;

draw_state<=init;

height_reg0<=0;

height_reg1<=0;

height_reg2<=0;

height_reg3<=0;

height_reg4<=0;

height_reg5<=0;

height_reg6<=0;

height_reg7<=0;

height_reg8<=0;

height_reg9<=0;

height_reg10<=0;

height_reg11<=0;

height_reg12<=0;

height_reg13<=0;

height_reg14<=0;

height_reg15<=0;

height_reg16<=0;

height_reg17<=0;

height_reg18<=0;

height_reg19<=0;

height_reg20<=0;

height_reg21<=0;

height_reg22<=0;

height_reg23<=0;

height_reg24<=0;

height_reg25<=0;

height_reg26<=0;

height_reg27<=0;

height_reg28<=0;

height_reg29<=0;

height_reg30<=0;

height_reg31<=0;

height_reg32<=0;

height_reg33<=0;

height_reg34<=0;

height_reg35<=0;

height_reg36<=0;

height_reg37<=0;

height_reg38<=0;

height_reg39<=0;

height_reg40<=0;

height_reg41<=0;

height_reg42<=0;

height_reg43<=0;

height_reg44<=0;

height_reg45<=0;

height_reg46<=0;

height_reg47<=0;

height_reg48<=0;

height_reg49<=0;

height_reg50<=0;

height_reg51<=0;

height_reg52<=0;

height_reg53<=0;

height_reg54<=0;

height_reg55<=0;

height_reg56<=0;

height_reg57<=0;

height_reg58<=0;

height_reg59<=0;

height_reg60<=0;

height_reg61<=0;

height_reg62<=0;

height_reg63<=0;

height_reg64<=0;

height_reg65<=0;

height_reg66<=0;

height_reg67<=0;

height_reg68<=0;

height_reg69<=0;

height_reg70<=0;

height_reg71<=0;

height_reg72<=0;

height_reg73<=0;

height_reg74<=0;

height_reg75<=0;

height_reg76<=0;

height_reg77<=0;

height_reg78<=0;

height_reg79<=0;

height_reg80<=0;

height_reg81<=0;

height_reg82<=0;

height_reg83<=0;

height_reg84<=0;

height_reg85<=0;

height_reg86<=0;

height_reg87<=0;

height_reg88<=0;

height_reg89<=0;

height_reg90<=0;

height_reg91<=0;

height_reg92<=0;

height_reg93<=0;

height_reg94<=0;

height_reg95<=0;

height_reg96<=0;

height_reg97<=0;

height_reg98<=0;

height_reg99<=0;

end

else begin

sampleCount <= sampleCount + 24'd1;

case(draw_state)

init: begin

if(sampleCount > period[13:0])begin

sampleCount <= 24'd0;

sampleAudio <= audIn;

sampleBass <= bass;

sampleCymbal <= cymbal;

sampleVoice <= voice;

end

case(sigSel[1:0])

2'd0: height_reg0 <= 10'd479-iHeight;

2'd1: height_reg0 <= 10'd479-bassH;

2'd2: height_reg0 <= 10'd479-cymbalH;

2'd3: height_reg0 <= 10'd479-voiceH;

endcase

height_reg1 <= height_reg0;

height_reg2 <= height_reg1;

height_reg3 <= height_reg2;

height_reg4 <= height_reg3;

height_reg5 <= height_reg4;

height_reg6 <= height_reg5;

height_reg7 <= height_reg6;

height_reg8 <= height_reg7;

height_reg9 <= height_reg8;

height_reg10 <= height_reg9;

height_reg11 <= height_reg10;

height_reg12 <= height_reg11;

height_reg13 <= height_reg12;

height_reg14 <= height_reg13;

height_reg15 <= height_reg14;

height_reg16 <= height_reg15;

height_reg17 <= height_reg16;

height_reg18 <= height_reg17;

height_reg19 <= height_reg18;

height_reg20 <= height_reg19;

height_reg21 <= height_reg20;

height_reg22 <= height_reg21;

height_reg23 <= height_reg22;

height_reg24 <= height_reg23;

height_reg25 <= height_reg24;

height_reg26 <= height_reg25;

height_reg27 <= height_reg26;

height_reg28 <= height_reg27;

height_reg29 <= height_reg28;

height_reg30 <= height_reg29;

height_reg31 <= height_reg30;

height_reg32 <= height_reg31;

height_reg33 <= height_reg32;

height_reg34 <= height_reg33;

height_reg35 <= height_reg34;

height_reg36 <= height_reg35;

height_reg37 <= height_reg36;

height_reg38 <= height_reg37;

height_reg39 <= height_reg38;

height_reg40 <= height_reg39;

height_reg41 <= height_reg40;

height_reg42 <= height_reg41;

height_reg43 <= height_reg42;

height_reg44 <= height_reg43;

height_reg45 <= height_reg44;

height_reg46 <= height_reg45;

height_reg47 <= height_reg46;

height_reg48 <= height_reg47;

height_reg49 <= height_reg48;

height_reg50 <= height_reg49;

height_reg51 <= height_reg50;

height_reg52 <= height_reg51;

height_reg53 <= height_reg52;

height_reg54 <= height_reg53;

height_reg55 <= height_reg54;

height_reg56 <= height_reg55;

height_reg57 <= height_reg56;

height_reg58 <= height_reg57;

height_reg59 <= height_reg58;

height_reg60 <= height_reg59;

height_reg61 <= height_reg60;

height_reg62 <= height_reg61;

height_reg63 <= height_reg62;

height_reg64 <= height_reg63;

height_reg65 <= height_reg64;

height_reg66 <= height_reg65;

height_reg67 <= height_reg66;

height_reg68 <= height_reg67;

height_reg69 <= height_reg68;

height_reg70 <= height_reg69;

height_reg71 <= height_reg70;

height_reg72 <= height_reg71;

height_reg73 <= height_reg72;

height_reg74 <= height_reg73;

height_reg75 <= height_reg74;

height_reg76 <= height_reg75;

height_reg77 <= height_reg76;

height_reg78 <= height_reg77;

height_reg79 <= height_reg78;

height_reg80 <= height_reg79;

height_reg81 <= height_reg80;

height_reg82 <= height_reg81;

height_reg83 <= height_reg82;

height_reg84 <= height_reg83;

height_reg85 <= height_reg84;

height_reg86 <= height_reg85;

height_reg87 <= height_reg86;

height_reg88 <= height_reg87;

height_reg89 <= height_reg88;

height_reg90 <= height_reg89;

height_reg91 <= height_reg90;

height_reg92 <= height_reg91;

height_reg93 <= height_reg92;

height_reg94 <= height_reg93;

height_reg95 <= height_reg94;

height_reg96 <= height_reg95;

height_reg97 <= height_reg96;

height_reg98 <= height_reg97;

height_reg99 <= height_reg98;

draw_state<=color;

end

color: begin

if((c0|c1|c2|c3|c4|c5|c6|c7|c8|c9|c10|c11|c12|c13|c14|c15|c16|c17|c18|c19|c20|c21|c22|c23|c24|c25|c26|c27|c28|c29|c30|c31|c32|c33|c34|c35|c36|c37|c38|c39|c40|c41|c42|c43|c44|c45|c46|c47|c48|c49|c50|c51|c52|c53|c54|c55|c56|c57|c58|c59|c60|c61|c62|c63|c64|c65|c66|c67|c68|c69|c70|c71|c72|c73|c74|c75|c76|c77|c78|c79|c80|c81|c82|c83|c84|c85|c86|c87|c88|c89|c90|c91|c92|c93|c94|c95|c96|c97|c98|c99) & ~(iY%10 ==0) | eye1 | eye2) begin

if (sigSel[4:2]==3'd0) begin

reg_R<=red;//10'h0;

reg_G<=green;//10'h0;

reg_B<=blue;//10'hfff;

end else if (sigSel[4:2]==3'd1) begin

reg_R <= sampleAudio[14:5];

reg_G <= ~sampleAudio[12:3];

reg_B <= sampleAudio[9:0];

end else if (sigSel[4:2]==3'd2) begin

reg_R <= sampleBass[14:5];

reg_G <= ~sampleBass[12:3];

reg_B <= sampleBass[9:0];

end else if (sigSel[4:2]==3'd3) begin

reg_R <= sampleCymbal[14:5];

reg_G <= ~sampleCymbal[12:3];

reg_B <= sampleCymbal[9:0];

end else if (sigSel[4:2]==3'd4) begin

reg_R <= sampleVoice[14:5];

reg_G <= ~sampleVoice[12:3];

reg_B <= sampleVoice[9:0];

end else begin

reg_R<=red;//10'h0;

reg_G<=green;//10'h0;

reg_B<=blue;//10'hfff;

end

if(eye1) begin

if (sigSel[4:2]==3'd0)begin

reg_R<=red;

reg_G<=green;

reg_B<=~blue;

end else if (sigSel[4:2]==3'd5) begin

reg_R<=~sampleBass[14:5];

reg_G<=~sampleCymbal[14:5];

reg_B<=~sampleVoice[14:5];

end else if (sigSel[4:2]==3'd6) begin

reg_R<=~sampleCymbal[14:5];

reg_G<=~sampleVoice[14:5];

reg_B<=~sampleBass[14:5];

end else if (sigSel[4:2]==3'd7) begin

reg_R<=~sampleVoice[14:5];

reg_G<=~sampleBass[14:5];

reg_B<=~sampleCymbal[14:5];

end

end

if(eye2) begin

if (sigSel[4:2]==3'd0)begin

reg_R<=red;

reg_G<=~green;

reg_B<=blue;

end else if (sigSel[4:2]==3'd5) begin

reg_R<=~bass[14:5];

reg_G<=~cymbal[14:5];

reg_B<=~voice[14:5];

end else if (sigSel[4:2]==3'd6) begin

reg_R<=~cymbal[14:5];

reg_G<=~voice[14:5];

reg_B<=~bass[14:5];

end else if (sigSel[4:2]==3'd7) begin

reg_R<=~voice[14:5];

reg_G<=~bass[14:5];

reg_B<=~cymbal[14:5];

end

end

end else begin // if not conditions are met

reg_R<=10'h0;

reg_G<=10'h0;

reg_B<=10'h0;

end

if(vs_sig) //finished drawing

draw_state<=init;

end

endcase

end //VGA sync

end //always

assign state=draw_state;

reg vs_state;

reg vs_sig;

always @ (posedge CLK) begin //generate a one cycle pulse on each v sync,signals a fully drawn screen

if(RST) begin

vs_state<=0;

end

else begin

case(vs_state)

0: begin

vs_sig<=0;

if(~iVGA_VS) begin

vs_sig<=1;

vs_state<=1;

end

end

1: begin

vs_sig<=0;

if(iVGA_VS)

vs_state<=0;

end

endcase

end

end

assign oR= reg_R;

assign oG= reg_G;

assign oB= reg_B;

endmodule

///////////////////////////////////////////////////////////////////

//////////////absolute values//////////////////////////////////////

///////////////////////////////////////////////////////////////////

module abs(out, in, dk_const, clk);

output reg signed [15:0] out ;

input wire signed [15:0] in ;

input wire [3:0] dk_const ;

input wire clk;

wire signed [17:0] new_out ;

//take absolute value and reduce amplitude

assign new_out = (in[15]?-in:in)>>dk_const;//out - (out>>>dk_const) + ((in[15]?-in:in)>>>dk_const) ;

always @(posedge clk)

begin

out <= new_out ;

end

endmodule

///////////////////////////////////////////////////////////////////

//////////// highest order bit find ///////////////////////////////

///////////////////////////////////////////////////////////////////

module firstHbit(in,out,CLK);

input CLK;

input [9:0] in;

output [9:0] out;

reg [9:0] out_reg;

always @ (posedge CLK) begin

if(in[9])

out_reg<=10'd479;

else if(in[8])

out_reg<=10'd360;

else if(in[7])

out_reg<=10'd320;

else if(in[6])

out_reg<=10'd280;

else if(in[5])

out_reg<=10'd240;

else if(in[4])

out_reg<=10'd200;

else if(in[3])

out_reg<=10'd160;

else if(in[2])

out_reg<=10'd120;

else if(in[1])

out_reg<=10'd80;

else if(in[0])

out_reg<=10'd40;

else

out_reg<=10'd0;

end //always

assign out=out_reg;

endmodule

///////////////////////////////////////////////////////////////////

//// signed mult of 2.16 format 2'comp ////////////////////////////

///////////////////////////////////////////////////////////////////

module signed_mult (out, a, b);

output [17:0] out;

input signed [17:0] a;

input signed [17:0] b;

wire signed [17:0] out;

wire signed [35:0] mult_out;

assign mult_out = a * b;

//assign out = mult_out[33:17];

assign out = {mult_out[35], mult_out[32:16]};

endmodule

///////////////////////////////////////////////////////////////////

/// Fourth order IIR filter ///////////////////////////////////////

///////////////////////////////////////////////////////////////////

module IIR4_18bit_fixed (audio_out, audio_in,

scale,

b1, b2, b3, b4, b5,

a2, a3, a4, a5,

state_clk, lr_clk, reset) ;

// The filter is a "Direct Form II Transposed"

//

// a(1)*y(n) = b(1)*x(n) + b(2)*x(n-1) + ... + b(nb+1)*x(n-nb)

// - a(2)*y(n-1) - ... - a(na+1)*y(n-na)

//

// If a(1) is not equal to 1, FILTER normalizes the filter

// coefficients by a(1).

//

// one audio sample, 16 bit, 2's complement

output reg signed [15:0] audio_out ;

// one audio sample, 16 bit, 2's complement

input wire signed [15:0] audio_in ;

// shift factor for output

input wire [2:0] scale ;

// filter coefficients

input wire signed [17:0] b1, b2, b3, b4, b5, a2, a3, a4, a5 ;

input wire state_clk, lr_clk, reset ;

/// filter vars //////////////////////////////////////////////////

wire signed [17:0] f1_mac_new, f1_coeff_x_value ;

reg signed [17:0] f1_coeff, f1_mac_old, f1_value ;

// input to filter

reg signed [17:0] x_n ;

// input history x(n-1), x(n-2)

reg signed [17:0] x_n1, x_n2, x_n3, x_n4 ;

// output history: y_n is the new filter output, BUT it is

// immediately stored in f1_y_n1 for the next loop through

// the filter state machine

reg signed [17:0] f1_y_n1, f1_y_n2, f1_y_n3, f1_y_n4 ;

// MAC operation

signed_mult f1_c_x_v (f1_coeff_x_value, f1_coeff, f1_value);

assign f1_mac_new = f1_mac_old + f1_coeff_x_value ;

// state variable

reg [3:0] state ;

//oneshot gen to sync to audio clock

reg last_clk ;

///////////////////////////////////////////////////////////////////

//Run the filter state machine FAST so that it completes in one

//audio cycle

always @ (posedge state_clk)

begin

if (reset)

begin

state <= 4'd15 ; //turn off the state machine

end

else begin

case (state)

1:

begin

// set up b1*x(n)

f1_mac_old <= 18'd0 ;

f1_coeff <= b1 ;

f1_value <= {audio_in, 2'b0} ;

//register input

x_n <= {audio_in, 2'b0} ;

// next state

state <= 4'd2;

end

2:

begin

// set up b2*x(n-1)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b2 ;

f1_value <= x_n1 ;

// next state

state <= 4'd3;

end

3:

begin

// set up b3*x(n-2)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b3 ;

f1_value <= x_n2 ;

// next state

state <= 4'd4;

end

4:

begin

// set up b4*x(n-3)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b4 ;

f1_value <= x_n3 ;

// next state

state <= 4'd5;

end

5:

begin

// set up b5*x(n-4)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b5 ;

f1_value <= x_n4 ;

// next state

state <= 4'd6;

end

6:

begin

// set up -a2*y(n-1)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a2 ;

f1_value <= f1_y_n1 ;

//next state

state <= 4'd7;

end

7:

begin

// set up -a3*y(n-2)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a3 ;

f1_value <= f1_y_n2 ;

//next state

state <= 4'd8;

end

8:

begin

// set up -a4*y(n-3)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a4 ;

f1_value <= f1_y_n3 ;

//next state

state <= 4'd9;

end

9:

begin

// set up -a5*y(n-4)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a5 ;

f1_value <= f1_y_n4 ;

//next state

state <= 4'd10;

end

10:

begin

// get the output

// and put it in the LAST output var

// for the next pass thru the state machine

//mult by four because of coeff scaling

// to prevent overflow

f1_y_n1 <= f1_mac_new<<scale ;

audio_out <= f1_y_n1[17:2] ;

// update output history

f1_y_n2 <= f1_y_n1 ;

f1_y_n3 <= f1_y_n2 ;

f1_y_n4 <= f1_y_n3 ;

// update input history

x_n1 <= x_n ;

x_n2 <= x_n1 ;

x_n3 <= x_n2 ;

x_n4 <= x_n3 ;

//next state

state <= 4'd15;

end

15:

begin

// wait for the audio clock and one-shot it

if (lr_clk && last_clk==1)

begin

state <= 4'd1 ;

last_clk <= 1'h0 ;

end

// reset the one-shot memory

else if (~lr_clk && last_clk==0)

begin

last_clk <= 1'h1 ;

end

end

default:

begin

// default state is end state

state <= 4'd15 ;

end

endcase

end

end

endmodule

///////////////////////////////////////////////////////////////////

//// signed mult of 3.24 format 2'comp/////////////////////////////

///////////////////////////////////////////////////////////////////

module signed_mult27 (out, a, b);

output [26:0] out;

input signed [26:0] a;

input signed [26:0] b;

wire signed [26:0] out;

wire signed [53:0] mult_out;

assign mult_out = a * b;

assign out = {mult_out[53], mult_out[50:24]};

endmodule

///////////////////////////////////////////////////////////////////

/// Fourth order IIR filter ///////////////////////////////////////

///////////////////////////////////////////////////////////////////

module IIR4_27bit (audio_out, audio_in,

scale,

b1, b2, b3, b4, b5,

a2, a3, a4, a5,

state_clk, lr_clk, reset) ;

// The filter is a "Direct Form II Transposed"

//

// a(1)*y(n) = b(1)*x(n) + b(2)*x(n-1) + ... + b(nb+1)*x(n-nb)

// - a(2)*y(n-1) - ... - a(na+1)*y(n-na)

//

// If a(1) is not equal to 1, FILTER normalizes the filter

// coefficients by a(1).

//

// one audio sample, 16 bit, 2's complement

output reg signed [15:0] audio_out ;

// one audio sample, 16 bit, 2's complement

input wire signed [15:0] audio_in ;

// shift factor for output

input wire [2:0] scale ;

// filter coefficients

input wire signed [26:0] b1, b2, b3, b4, b5, a2, a3, a4, a5 ;

input wire state_clk, lr_clk, reset ;

/// filter vars //////////////////////////////////////////////////

wire signed [26:0] f1_mac_new, f1_coeff_x_value ;

reg signed [26:0] f1_coeff, f1_mac_old, f1_value ;

// input to filter

reg signed [26:0] x_n ;

// input history x(n-1), x(n-2)

reg signed [26:0] x_n1, x_n2, x_n3, x_n4 ;

// output history: y_n is the new filter output, BUT it is

// immediately stored in f1_y_n1 for the next loop through

// the filter state machine

reg signed [26:0] f1_y_n1, f1_y_n2, f1_y_n3, f1_y_n4 ;

// MAC operation

signed_mult27 f1_c_x_v (f1_coeff_x_value, f1_coeff, f1_value);

assign f1_mac_new = f1_mac_old + f1_coeff_x_value ;

// state variable

reg [3:0] state ;

//oneshot gen to sync to audio clock

reg last_clk ;

///////////////////////////////////////////////////////////////////

//Run the filter state machine FAST so that it completes in one

//audio cycle

always @ (posedge state_clk)

begin

if (reset)

begin

state <= 4'd15 ; //turn off the state machine

end

else begin

case (state)

1:

begin

// set up b1*x(n)

f1_mac_old <= 27'd0 ;

f1_coeff <= b1 ;

f1_value <= {audio_in, 11'b0} ;

//register input

x_n <= {audio_in, 11'b0} ;

// next state

state <= 4'd2;

end

2:

begin

// set up b2*x(n-1)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b2 ;

f1_value <= x_n1 ;

// next state

state <= 4'd3;

end

3:

begin

// set up b3*x(n-2)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b3 ;

f1_value <= x_n2 ;

// next state

state <= 4'd4;

end

4:

begin

// set up b4*x(n-3)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b4 ;

f1_value <= x_n3 ;

// next state

state <= 4'd5;

end

5:

begin

// set up b5*x(n-4)

f1_mac_old <= f1_mac_new ;

f1_coeff <= b5 ;

f1_value <= x_n4 ;

// next state

state <= 4'd6;

end

6:

begin

// set up -a2*y(n-1)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a2 ;

f1_value <= f1_y_n1 ;

//next state

state <= 4'd7;

end

7:

begin

// set up -a3*y(n-2)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a3 ;

f1_value <= f1_y_n2 ;

//next state

state <= 4'd8;

end

8:

begin

// set up -a4*y(n-3)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a4 ;

f1_value <= f1_y_n3 ;

//next state

state <= 4'd9;

end

9:

begin

// set up -a5*y(n-4)

f1_mac_old <= f1_mac_new ;

f1_coeff <= a5 ;

f1_value <= f1_y_n4 ;

//next state

state <= 4'd10;

end

10:

begin

// get the output

// and put it in the LAST output var

// for the next pass thru the state machine

//mult by four because of coeff scaling

// to prevent overflow

f1_y_n1 <= f1_mac_new<<scale ;

audio_out <= f1_y_n1[26:11] ;

// update output history

f1_y_n2 <= f1_y_n1 ;

f1_y_n3 <= f1_y_n2 ;

f1_y_n4 <= f1_y_n3 ;

// update input history

x_n1 <= x_n ;

x_n2 <= x_n1 ;

x_n3 <= x_n2 ;

x_n4 <= x_n3 ;

//next state

state <= 4'd15;

end

15:

begin

// wait for the audio clock and one-shot it

if (lr_clk && last_clk==1)

begin

state <= 4'd1 ;

last_clk <= 1'h0 ;

end

// reset the one-shot memory

else if (~lr_clk && last_clk==0)

begin

last_clk <= 1'h1 ;

end

end

default:

begin

// default state is end state

state <= 4'd15 ;

end

endcase

end

end

endmodule

///////////////////////////////////////////////////////////////////

///////////////////// Pixel Value Controller //////////////////////

///////////////////////////////////////////////////////////////////

module pixelController(reset, schemeReset, CLK, CLK27, AUDCLK, VGA_VS, VGA_HS, audIn, periodIn, red, green, blue);

//inputs

input reset, VGA_VS, VGA_HS, CLK, CLK27, AUDCLK;

input [7:0] schemeReset;

input signed [15:0] audIn;

input [31:0] periodIn;

//registers

reg [1:0] wtPrd;

reg [31:0] realPeriod;

reg [7:0] schemeCycle;

reg [31:0] schemeCount;

//outputs

output [9:0] red, green, blue;

//output [31:0] periodOut;

//wires

wire [9:0] redValue, greenValue, blueValue;

//wire [31:0] period;

//waveform period calculator

//periodCalc calcUnit1(CLK, CLK27, AUDCLK, clk1000, audIn, period);

//pixel variation unit

pixelVar unit1(reset, VGA_VS, CLK, schemeCycle, wtPrd, realPeriod, redValue, greenValue, blueValue);

//scheme logic

always @ (posedge CLK) begin

if (reset) begin

schemeCount <= 32'd0;

schemeCycle <= schemeReset;

end else begin

// scheme cycler

schemeCount <= schemeCount + 32'd1;

if(schemeCount > (periodIn<<4)) begin//32'd90000000)begin

schemeCount <= 32'd0;

//schemeSubCount <= schemeSubCount + 20'd1;

schemeCycle <= schemeCycle + 8'd1;

if (schemeCycle > 8'd254) begin//(schemeCycle > 8'd255) begin

schemeCycle <= 8'd0;

wtPrd <= wtPrd + 2'd1;

if (wtPrd == 2'd3) begin

wtPrd <= 2'd0;

schemeCycle <= schemeCycle + 8'd1;

end

end

end

end

realPeriod <= (periodIn>>5);

end

//assign outputs

assign red = redValue;

assign green = greenValue;

assign blue = blueValue;

//assign periodOut = period;

endmodule

///////////////////////////////////////////////////////////////////

///////////// CIC N=2 M=1 filter //////////////////////////////////

///////////////////////////////////////////////////////////////////

module CIC_N2_M1_16bit_fixed (audio_out, rf_in,

rf_clk, lr_clk, reset) ;

// The filter is a

// double integrator/comb CIC filter

//

// one audio sample, 16 bit, 2's complement

output reg signed [15:0] audio_out ;

input signed [15:0] rf_in ;

input wire rf_clk, lr_clk, reset ;

reg signed [39:0] integrator1, comb1 ; //[39:0]

reg signed [39:0] integrator2, comb2, temp_int2 ;

wire signed [39:0] running_sum1, running_sum2 ;

always @(posedge rf_clk)

begin

if (reset)

begin

integrator1 <= 40'd0 ;

integrator2 <= 40'd0 ;

end

else

begin

integrator1 <= integrator1 + { {24{rf_in[15]}}, rf_in} ;

integrator2 <= integrator2 + integrator1 ;

end

end

always @(posedge lr_clk)

begin

temp_int2 <= integrator2 ;

comb1 <= temp_int2 ;

comb2 <= running_sum1 ;

audio_out <= running_sum2[35:20];

end

assign running_sum1 = temp_int2 - comb1 ;

assign running_sum2 = running_sum1 - comb2 ;

endmodule

///////////////////////////////////////////////////////////////////

////////////////////// Pixel Color Variation Unit /////////////////

///////////////////////////////////////////////////////////////////

module pixelVar(reset, VGA_VS, CLK, scheme, wtPer, period, red, green, blue);

//inputs

input CLK, reset, VGA_VS;

input [1:0] wtPer;

input [8:0] scheme;

input [31:0] period;

//registers

reg reverse; // reverse the order in which operation is done

reg stat; //stationay second color

reg alt; //second color alternates

reg sync; //synchronize with VGA_VS or not

reg [1:0] thirdVal;

reg [2:0] mode;

reg [2:0] maxCount;

reg [15:0] counter;

reg [31:0] countMax;

reg [9:0] redVal, blueVal, greenVal;

//outputs

output [9:0] red, green, blue;

always @ (posedge CLK) begin

sync <= scheme[8];

if (reset) begin//if system is reset

redVal <= 10'd0;

greenVal <= 10'd0;

blueVal <= 10'd0;

counter <= 16'd0;

end else if (~VGA_VS) begin

mode <= scheme[7:5];

reverse <= scheme[4];

thirdVal <= scheme[3:2];

stat <= scheme[1];

alt <= scheme[0];

counter <= counter + 16'd1;//increment count

//set count max - different wait periods to cycle colors

case(wtPer)

2'd0: countMax <= period<<3; // 8x bass beat (2x whole note)

2'd1: countMax <= period<<2; // 4x bass beat (whole note)

2'd2: countMax <= period<<1; // 2x bass beat (half note)

2'd3: countMax <= period;//bass beat (quarter note)

endcase

//select color shifting mode

case(mode)

3'd0: begin // red up, green down (reverse is direction switch)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if(reverse) begin

if (redVal < 10'd1020) begin

redVal <= redVal + 10'd10;

end else begin

redVal <= 10'd0;

end

end else begin

if (redVal > 10'd0) begin

redVal <= redVal - 10'd10;

end else begin

redVal <= 10'd1020;

end

end

//green value

if (~stat) begin //stationary second color

if (reverse) begin

if (greenVal > 10'd0) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end else begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end

if (alt && maxCount>3) begin //alternate third color

maxCount <= 3'd0;

if (blueVal==10'd1000) begin //reset third color at 1000

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end else begin//set third color to constant value

case(thirdVal)

2'd0: blueVal <= 10'd0;

2'd1: blueVal <= 10'd250;

2'd2: blueVal <= 10'd500;

2'd3: blueVal <= 10'd750;

endcase

end

end else begin

if (alt && maxCount>3) begin //alternate second color

maxCount <= 3'd0;

if (greenVal==10'd1000) begin //reset second color at 1000

greenVal <= 10'd0;

end else begin

greenVal <= greenVal + 10'd200;

end

end

end //stat check

end //end count check

end //end of this case

3'd1: begin //blue up, red down (reverse is direction switch)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if(reverse) begin

if (blueVal < 10'd1020) begin

blueVal <= blueVal + 10'd10;

end else begin

blueVal <= 10'd0;

end

end else begin

if (blueVal > 10'd0) begin

blueVal <= blueVal - 10'd10;

end else begin

blueVal <= 10'd1020;

end

end

//green value

if (~stat) begin //stationary second color

if (reverse) begin

if (redVal > 10'd0) begin

redVal <= redVal - 10'd10;

end else begin

redVal <= 10'd1020;

end

end else begin

if (redVal < 10'd1020) begin

redVal <= redVal + 10'd10;

end else begin

redVal <= 10'd0;

end

end

if (alt && maxCount>3) begin //alternate third color

maxCount <= 3'd0;

if (greenVal==10'd1000) begin //reset third color at 1000

greenVal <= 10'd0;

end else begin

greenVal <= greenVal + 10'd200;

end

end else begin//set third color to constant value

case(thirdVal)

2'd0: greenVal <= 10'd0;

2'd1: greenVal <= 10'd250;

2'd2: greenVal <= 10'd500;

2'd3: greenVal <= 10'd750;

endcase

end

end else begin

if (alt && maxCount>3) begin //alternate second color

maxCount <= 3'd0;

if (redVal==10'd1000) begin //reset second color at 1000

redVal <= 10'd0;

end else begin

redVal <= redVal + 10'd200;

end

end

end //stat check

end //end count check

end//end of this case

3'd2: begin //green up, blue down (reverse is direction switch)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if(reverse) begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end else begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end

//green value

if (~stat) begin //stationary second color

if (reverse) begin

if (blueVal > 10'd0) begin

blueVal <= blueVal - 10'd10;

end else begin

blueVal <= 10'd1020;

end

end else begin

if (blueVal < 10'd1020) begin

blueVal <= blueVal + 10'd10;

end else begin

blueVal <= 10'd0;

end

end

if (alt && maxCount>3) begin //alternate third color

maxCount <= 3'd0;

if (redVal==10'd1000) begin //reset third color at 1000

redVal <= 10'd0;

end else begin

redVal <= redVal + 10'd200;

end

end else begin//set third color to constant value

case(thirdVal)

2'd0: redVal <= 10'd0;

2'd1: redVal <= 10'd250;

2'd2: redVal <= 10'd500;

2'd3: redVal <= 10'd750;

endcase

end

end else begin

if (alt && maxCount>3) begin //alternate second color

maxCount <= 3'd0;

if (blueVal==10'd1000) begin //reset second color at 1000

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end

end //stat check

end //end count check

end//end of this case

3'd3: begin //blue up, green down (reverse is direction switch)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if(reverse) begin

if (blueVal < 10'd1020) begin

blueVal <= blueVal + 10'd10;

end else begin

blueVal <= 10'd0;

end

end else begin

if (blueVal > 10'd0) begin

blueVal <= blueVal - 10'd10;

end else begin

blueVal <= 10'd1020;

end

end

//green value

if (~stat) begin //stationary second color

if (reverse) begin

if (greenVal > 10'd0) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end else begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end

if (alt && maxCount>3) begin //alternate third color

maxCount <= 3'd0;

if (redVal==10'd1000) begin //reset third color at 1000

redVal <= 10'd0;

end else begin

redVal <= redVal + 10'd200;

end

end else begin//set third color to constant value

case(thirdVal)

2'd0: redVal <= 10'd0;

2'd1: redVal <= 10'd250;

2'd2: redVal <= 10'd500;

2'd3: redVal <= 10'd750;

endcase

end

end else begin

if (alt && maxCount>3) begin //alternate second color

maxCount <= 3'd0;

if (greenVal==10'd1000) begin //reset second color at 1000

greenVal <= 10'd0;

end else begin

greenVal <= greenVal + 10'd200;

end

end

end //stat check

end //end count check

end//end of this case

3'd4: begin //green up, red down (reverse is direction switch)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if(reverse) begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end else begin

if (greenVal > 10'd0) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end

//green value

if (~stat) begin //stationary second color

if (reverse) begin

if (redVal > 10'd0) begin

redVal <= redVal - 10'd10;

end else begin

redVal <= 10'd1020;

end

end else begin

if (redVal < 10'd1020) begin

redVal <= redVal + 10'd10;

end else begin

redVal <= 10'd0;

end

end

if (alt && maxCount>3) begin //alternate third color

maxCount <= 3'd0;

if (blueVal==10'd1000) begin //reset third color at 1000

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end else begin//set third color to constant value

case(thirdVal)

2'd0: blueVal <= 10'd0;

2'd1: blueVal <= 10'd250;

2'd2: blueVal <= 10'd500;

2'd3: blueVal <= 10'd750;

endcase

end

end else begin

if (alt && maxCount>3) begin //alternate second color

maxCount <= 3'd0;

if (redVal==10'd1000) begin //reset second color at 1000

redVal <= 10'd0;

end else begin

redVal <= redVal + 10'd200;

end

end

end //stat check

end //end count check

end//end of this case

3'd5: begin //red up, green up (reverse is both down)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if (~reverse) begin

if(redVal < 10'd1020) begin

redVal <= redVal + 10'd10;

end else begin

redVal <= 10'd0;

end

end else begin

if (redVal > 10'd0) begin

redVal <= redVal - 10'd10;

end else begin

redVal <= 10'd1020;

end

end

//green value

if (stat) begin //stationary second color

if (alt) begin //alternate second color

if (maxCount>3) begin

maxCount <= 3'd0;

if (greenVal==10'd1000) begin

greenVal <= 10'd0;

end else begin

greenVal <= greenVal + 10'd200;

end

end

end

end else begin

if (reverse) begin

if ( greenVal > 10'd0) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end else begin

if (greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end

if (alt & maxCount>3) begin //alternate third color

if (maxCount>3) begin

maxCount <= 3'd0;

if (blueVal==10'd1000)begin

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end

end else begin

//set third color to constant value

case(thirdVal)

2'd0: blueVal <= 10'd0;

2'd1: blueVal <= 10'd250;

2'd2: blueVal <= 10'd500;

2'd3: blueVal <= 10'd750;

endcase

end

end

end

end

3'd6: begin // red up, blue up (reverse is both down)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if (~reverse) begin

if(redVal < 10'd1020) begin

redVal <= redVal + 10'd10;

end else begin

redVal <= 10'd0;

end

end else begin

if (redVal > 10'd0) begin

redVal <= redVal - 10'd10;

end else begin

redVal <= 10'd1020;

end

end

//green value

if (stat) begin //stationary second color

if (alt) begin //alternate second color

if (maxCount>3) begin

maxCount <= 3'd0;

if (blueVal==10'd1000) begin

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end

end

end else begin

if (reverse) begin

if ( blueVal > 10'd0) begin

blueVal <= blueVal - 10'd10;

end else begin

blueVal <= 10'd1020;

end

end else begin

if (blueVal < 10'd1020) begin

blueVal <= blueVal + 10'd10;

end else begin

blueVal <= 10'd0;

end

end

if (alt & maxCount>3) begin //alternate third color

if (maxCount>3) begin

maxCount <= 3'd0;

if (greenVal==10'd1000)begin

greenVal <= 10'd0;

end else begin

greenVal <= greenVal + 10'd200;

end

end

end else begin

//set third color to constant value

case(thirdVal)

2'd0: greenVal <= 10'd0;

2'd1: greenVal <= 10'd250;

2'd2: greenVal <= 10'd500;

2'd3: greenVal <= 10'd750;

endcase

end

end

end

end

3'd7: begin //green up, blue up (reverse is both down)

//different wait period to cycle colors

if (counter > countMax) begin

maxCount <= maxCount + 3'd1;

counter <= 16'd0;

//red value

if (~reverse) begin

if(greenVal < 10'd1020) begin

greenVal <= greenVal + 10'd10;

end else begin

greenVal <= 10'd0;

end

end else begin

if (greenVal > 10'd0) begin

greenVal <= greenVal - 10'd10;

end else begin

greenVal <= 10'd1020;

end

end

//green value

if (stat) begin //stationary second color

if (alt) begin //alternate second color

if (maxCount>3) begin

maxCount <= 3'd0;

if (blueVal==10'd1000) begin

blueVal <= 10'd0;

end else begin

blueVal <= blueVal + 10'd200;

end

end

end

end else begin

if (reverse) begin

if ( blueVal > 10'd0) begin

blueVal <= blueVal - 10'd10;

end else begin

blueVal <= 10'd1020;

end

end else begin

if (blueVal < 10'd1020) begin

blueVal <= blueVal + 10'd10;

end else begin

blueVal <= 10'd0;

end

end

if (alt & maxCount>3) begin //alternate third color

if (maxCount>3) begin

maxCount <= 3'd0;

if (redVal==10'd1000)begin

redVal <= 10'd0;

end else begin

redVal <= redVal + 10'd200;

end

end

end else begin

//set third color to constant value

case(thirdVal)

2'd0: redVal <= 10'd0;

2'd1: redVal <= 10'd250;

2'd2: redVal <= 10'd500;

2'd3: redVal <= 10'd750;

endcase

end

end

end

end

endcase

end//end VGA_VS

end//end always

assign red = redVal;

assign blue = blueVal;

assign green = greenVal;

endmodule

///////////////////////////////////////////////////////////////////

// Decode one hex digit for LED 7-seg display /////////////////////

///////////////////////////////////////////////////////////////////

module HexDigit(segs, num);

input [3:0] num ; //the hex digit to be displayed

output [6:0] segs ; //actual LED segments

reg [6:0] segs ;

always @ (num)

begin

case (num)

4'h0: segs = 7'b1000000;

4'h1: segs = 7'b1111001;

4'h2: segs = 7'b0100100;

4'h3: segs = 7'b0110000;

4'h4: segs = 7'b0011001;

4'h5: segs = 7'b0010010;

4'h6: segs = 7'b0000010;

4'h7: segs = 7'b1111000;

4'h8: segs = 7'b0000000;

4'h9: segs = 7'b0010000;

4'ha: segs = 7'b0001000;

4'hb: segs = 7'b0000011;

4'hc: segs = 7'b1000110;

4'hd: segs = 7'b0100001;

4'he: segs = 7'b0000110;

4'hf: segs = 7'b0001110;

default segs = 7'b1111111;

endcase

end

endmodule

///////////////////////////////////////////////////////////////////

///////////////////// Box visualization ///////////////////////////

///////////////////////////////////////////////////////////////////

module boxVisual(reset, CLK50, AUDCLK, VGA_VS, VGA_HS, audIn, cymbal, bass, voice, coordX, coordY, period, red, green, blue);

// parameters

parameter locate=1'd0, color=1'd1;

// inputs

input reset, CLK50, AUDCLK, VGA_VS, VGA_HS;

input [15:0] audIn, cymbal, bass, voice;

input [8:0] coordX, coordY;

input [31:0] period;

//regs

reg state;

reg [15:0] sample, sampleCymbal, sampleBass, sampleVoice;

reg [2:0] region;