|

|

先说我程序的目的:用FPGA循环输出8位数字量。用了外部晶振提供CLK,三个拨动开关R0,R1,R2,控制输出数据,数据在CLK上升沿输出。还有一个复位按钮,高电平复位。

程序一:

module DM412(CLK,rst,DAI,R0,R1,R2)

input CLK,,rst,R0,R1,R2;

output DAI;

reg[7:0] DAI,J;

reg DATA;

lways @ (posedge CLK or posedge rst)

if(rst)

begin DATA<=1'b0;end

else

begin

DATA = (R0)?8'b00000000 // R0,R1,R2选择8位输出数据

:((R1)?8'b10101010

:((R2)?8'b11111111));

end

always @ (posedge CLK or posedge rst)

if(rst)

begin DAI<=1'b0;

J<=1'b0;

end

else

begin DAI<=DATA[7-J];// 这样的为什么都不行,仿真结果每个CLK上升沿输出的数据都是是DAI=DATA[7],完全无视J的存在! 这样的为什么都不行,仿真结果每个CLK上升沿输出的数据都是是DAI=DATA[7],完全无视J的存在!

J<=J+1'b1;

end

endmodule

程序一:// 这是个超级废品!

module DM412(CLK,rst,DAI,R0,R1,R2)

input CLK,,rst,R0,R1,R2;

output DAI;

reg[7:0] DAI;

reg DATA;

lways @ (posedge CLK or posedge rst)

if(rst)

begin DATA<=1'b0;end

else

begin

DATA = (R0)?8'b00000000 // R0,R1,R2

:((R1)?8'b10101010

:((R2)?8'b11111111));

end

always @ (posedge CLK or posedge rst)

if(rst)

begin DAI<=1'b0;end

else

begin DAI<=DATA[7];

DATA<=DATA<<1;//  DATA左移一位, 问题是输完8次后数据不是会全变0了吗? 我是想要循环输出的啊,怎么办? DATA左移一位, 问题是输完8次后数据不是会全变0了吗? 我是想要循环输出的啊,怎么办?

end

endmodule

/*=ERROR===提示错误:DATA不能多次赋值,会产生竞争,但是我这里既要想既要给DATA赋初值,又要变化它 怎么办? ======*/ ======*/

程序二://为了改变程序二的错误 写了这个,还是失败的说!

module DM412(CLK,rst,DAI,R0,R1,R2)

input CLK,,rst,R0,R1,R2;

output DAI,;

reg[7:0] DAI,DATA0;

wire DATA;

lways @ (posedge CLK or posedge rst)

if(rst)

begin DATA<=1'b0;end

else

begin

DATA = (R0)?8'b00000000 // R0,R1,R2

:((R1)?8'b10101010

:((R2)?8'b11111111));

end

always @ (posedge CLK or posedge rst)

if(rst)

begin DAI<=1'b0;end

else

begin

DATA[7:0]<=({DATA[0],DATA[7:1]}) // 这样可以让数据循环??? 我听说的。

DAI<=DATA0[7];

end

endmodule

/*======  ========我只是想写一个如此简单的程序 为什么都不行呢? 高手来帮忙了。 ========我只是想写一个如此简单的程序 为什么都不行呢? 高手来帮忙了。

R0,R1,R2本来可以组成8种状态,这样就可以选择8种DATA[7:0],可以用case语句来给========================*/

always@(R1 or R2 or R3)//在同一个程序中的不同always中,可以分别有电平和上升沿的触发吗?我知道在同一个always中不能同时有。

if(rst)

begin DATA<=1'b0; end

else

begin

case({R2,R1,R0})

3'b000:begin DATA<=8'b00000000; end

3'b001:begin DATA<=8'b00000000; end

3'b010:begin DATA<=8'b00000000; end

3'b011:begin DATA<=8'b00000000; end

3'b100:begin DATA<=8'b00000000; end

3'b101:begin DATA<=8'b00000000; end

3'b110:begin DATA<=8'b00000000; end

default:begin DATA<=8'b00000000; end

endcase

end

/*==============上面这段可以吗?============================*/

/*=====  =数据的循环给到底要怎么给,坐等高手来解答,多照顾下新手哈= =数据的循环给到底要怎么给,坐等高手来解答,多照顾下新手哈= ==============*/ ==============*/

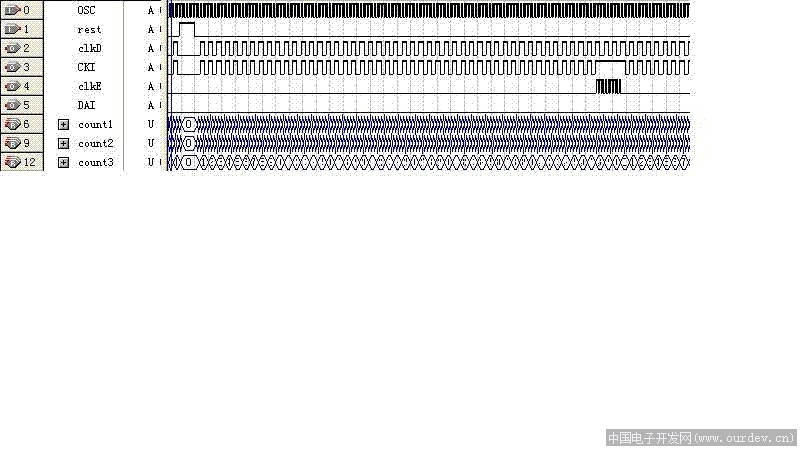

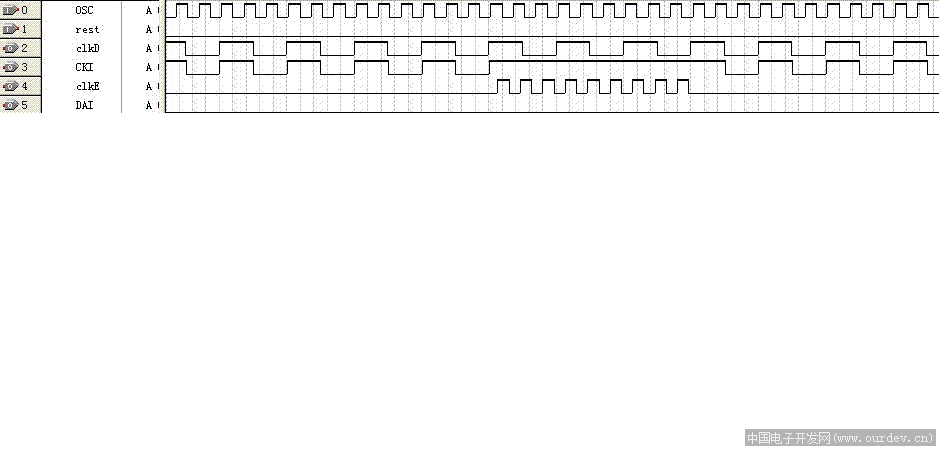

/*===下面这个是好的哈, 时序图,将60MHZ的外部晶振OSC进行3分频得到20MHZ的时钟clkD,由clkD再整出CKI来,CKI的要求是48个上升沿后保持三个周期的高电平,然后循环。 48位数据就是在CKI上升沿时给,给完48位后在三个周期的高电平阶段,数据给8个脉冲。然后循环。

现在我主要就是差的给数据!! =============================*/ =============================*/

module DM(OSC,rest,STI_I,DAI_I,SDO_I,POL_I,CKI,STI,DAI,SDO,POL,clkD,clkE,R0,R1,R2); //clk这些放这里只是为了仿真时看,***_I的都还没有用到。

input OSC,STI_I,rest,DAI_I,SDO_I,POL_I,R0,R1,R2;

output CKI,DAI,SDO,POL,STI,clkD,clkE;

reg[3:0] count1,count2;

reg[8:0] count3;

reg clkA,clkB,clkC;

wire clk_re;

wire CKI,clkD,clkE;

reg [6:0] J;

reg [2:0] T;

reg [9:0] K;

reg DAI,STI;

/*==========================================*/

wire [47:0] DATA;

reg [47:0] DATA1;

reg CKI_RE;

wire R0,R1,R2;

assign DATA=48'HF0F;

/*================================================*/

parameter N = 3; /*N分频*/

assign clk_re = ~OSC;

/*=================================CKI=======================*/

assign clkE = clkC & OSC & CKI; // ======8 MAICHONG===

assign clkD = clkA | clkB; // =========20 MHZ=====

assign CKI = clkD | clkC;

always @(posedge OSC)

if( rest)

begin

count1 <= 1'b0;

clkA <= 1'b0;

end

else

if(count1 < (N - 1))

begin

count1 <= count1 + 1'b1; /*这里是阻塞赋值是先执行了下面的IF判断,最后才赋的值。最初看这程序时没注意,想了好半天*/

if(count1 == (N - 1)/2)

begin

clkA <= ~clkA;

end

end

else

begin

clkA <= ~clkA;

count1 <= 1'b0;

end

always @ (posedge clk_re)

if( rest)

begin

count2 <= 1'b0;

clkB <= 1'b0;

end

else

if(count2 < (N - 1))

begin

count2 <= count2 + 1'b1;

if(count2 == (N - 1)/2)

begin

clkB <= ~clkB;

end

end

else

begin

clkB <= ~clkB;

count2 <= 1'b0;

end

/*========================================================*/

always @(posedge clkD or posedge rest )

if( rest)

begin

count3 <= 1'b0;

end

else

if(count3<50)

begin

count3<=count3+1'b1;

end

else begin

count3<=1'b0;

end

always @(posedge clkD)

if( rest)

begin

clkC<= 1'b0;

end

else if(count3<47)

begin clkC<=1'b0;end

else if(count3==50)

begin clkC<=1'b0;end

else begin clkC<=1'b1; end

endmudule

结果:

(原文件名:1.GIF)

(原文件名:2.GIF)

中间有9个脉冲,因为是三分频 只能是3的倍数,其实要求的DAI是8个脉冲能启动自动锁存的功能,但9个应该也可以吧 , 我只能做到这份上 。 呜呜呜~~

总得来说,我就是不知道怎么循环给数据,您要是能看完整个帖子,我就知足了~~~~~~ ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|