|

|

module cd16

(

input start ,

input clk,

input rst,

input [7:0] dat_i,

output reg e,

output reg rw,

output reg di,

output reg[7:0] dat

);

parameter DIV_WORK_CLOCK = 6600;//产生10kHz信号控制lcd.e,设置为100kHz时复位不灵敏

parameter DIV_WORK_CLOCK_WIDTH = 16;

//wire p_clk ;

//reg[wigth-1:0] clk_e_counter ;

reg [3:0] state ;

reg [3:0] instruction_state ;

reg [3:0] instruction_next_state ;

reg [9:0] instruction[3:0] ;

reg instruction_set ;

reg [3:0] instruction_length ;

reg [3:0] instruction_index ;

wire [9:0] action_struction ;

wire p_clk_e;//10kHz

reg[DIV_WORK_CLOCK_WIDTH-1:0] clk_e_counter;

assign action_struction = instruction[instruction_length-1-instruction_index] ;

assign p_clk_e = (clk_e_counter==0)?1'B1:1'B0;

always@(posedge clk,negedge rst,posedge instruction_set)

begin

if(rst == 0)

begin

e <= 0 ;

rw <= 0 ;

di <= 0 ;

//instruction_set <= 0 ;

state <= 0 ;

end

else if(instruction_set == 1'B1)

begin

//instruction_set <= 0 ;

instruction_index <= instruction_length - 1'B1 ;

end

else if(clk == 1'B1)

begin

case(state)

4'd0 :

begin

e <= 0 ;

rw <= 0 ;

di <= 0 ;

if(instruction_length > 0)

begin

state <= 4'd1 ;

end

end

4'd1:

begin

di <= action_struction[9] ;

rw <= action_struction[8] ;

dat <= action_struction[7:0] ;

state <= 4'd2 ;

end

4'd2:

begin

e <= 0 ;

if(p_clk_e == 1'b1)

begin

state <= 4'd3 ;

end

end

4'd3:

begin

e <= 1'b1 ;

if(p_clk_e == 1'b1)

begin

state <= 4'd4 ;

end

end

4'd4:

begin

e <= 0 ;

if(p_clk_e == 1'b1)

begin

if(instruction_index == 1'B0)

begin

state <= 4'd5 ;

end

else

begin

instruction_index <= instruction_index - 1'b1 ;

state <= 4'd1 ;

end

end

end

4'd5:

begin

if(instruction_length == 0)

state <= 4'd0 ;

end

default: state <= 4'd0 ;

endcase

end

end

always@(posedge clk,negedge rst)

begin

if(rst == 0)

begin

instruction_length <= 0 ;

instruction_set <= 0 ;

instruction_state <= 4'd1 ;

end

else if(clk == 1'b1)

begin

case(instruction_state)

4'd0:

begin

if(start == 1'b1) instruction_state <= 4'd4;

end

4'd1:

begin

instruction[0] <= 10'b0000110000 ;

instruction[1] <= 10'b0000001111 ;

instruction[2] <= 10'b0000000110 ;

instruction[3] <= 10'b0000000001 ;

instruction_length <= 4 ;

instruction_set <= 1'b1 ;

instruction_next_state <= 4'd0;

instruction_state <=4'd2 ;

end

4'd2:

begin

instruction_set <= 1'B0 ;

instruction_state <=4'd3 ;

end

4'd3:

begin

if(start == 1'b0)

instruction_state <= instruction_next_state ;

end

4'd4:

begin

instruction[0] <= {2'b10,dat_i} ;

instruction_length <= 1 ;

instruction_set <= 1'b1 ;

instruction_next_state <= 4'd0 ;

instruction_state <= 4'd2 ;

end

default:

instruction_state <= 4'd0 ;

endcase

end

end

always@(negedge clk, negedge rst)

begin

if (rst == 1'B0)

clk_e_counter <= 0;

else if(clk == 1'B0)

begin

if (clk_e_counter == DIV_WORK_CLOCK-1'B1)

clk_e_counter <= 0;

else

clk_e_counter <= clk_e_counter+1'B1;

end

end

endmodule

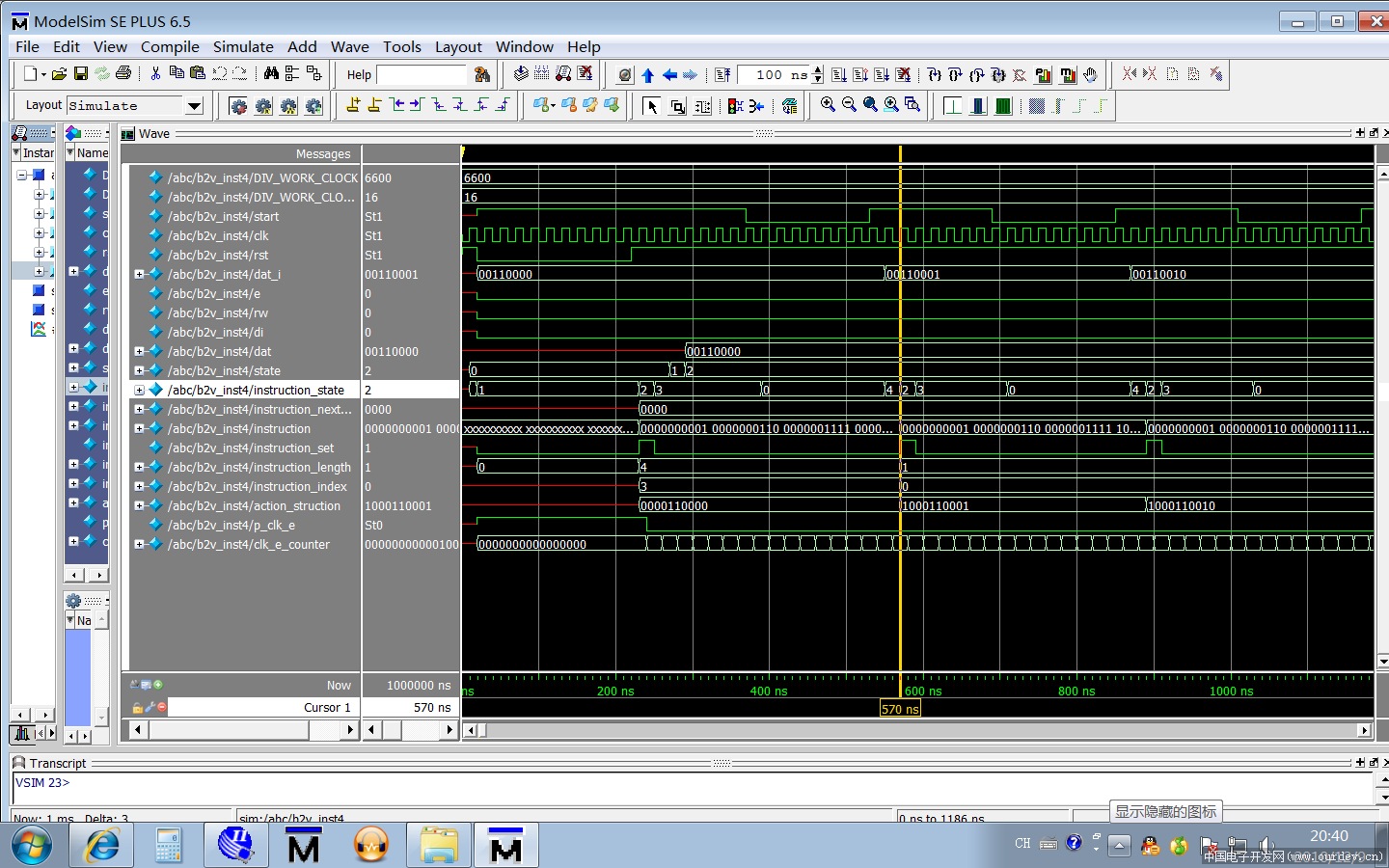

(原文件名:shixu2.png)

仿真光标所指处,两个状态机分别执行到了state=4'd2,instruction_state=4'd2。但是奇怪instruction_index怎么会变成0的? |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|