|

|

module dddd(clk_in,clr,key,L1,L2);

input clk_in,key,clr;

output L1,L2;

reg L1,L2;

reg[7:0] q;

reg state;

always @(posedge clk_in )

if(!clr)

begin

q=0;

L1=1;

L2=1;

state=1;

end

else

case(state)

1'b0:

begin

L1=0;

L2=1;

if(q<8'd40)

begin

if(led_ctrl)

state=1'b1;

else

q=q+1;

end

else

begin

q=0;

L1=~L1;

L2=~L2;

end

end

1'b1:

begin

L1=1;

L2=1;

q=0;

if(led_ctrl)

state=1'b0;

else

state=1'b1;

end

endcase

//------------------------------------------------------

reg [3:0] cnt; //计数寄存器

always @ (posedge clk_in)

if (!clr) //异步复位

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

reg low_sw;

always @(posedge clk_in)

if (!clr)

low_sw <= 1'b1;

else if (cnt == 4'd10) //满20ms,将按键值锁存到寄存器low_sw中

low_sw <= key;

// ---------------------------------------------------------------------------

reg low_sw_r; //每个时钟周期的上升沿将low_sw信号锁存到low_sw_r中

always @ ( posedge clk_in)

if (!clr)

low_sw_r <= 1'b1;

else

low_sw_r <= low_sw;

//当寄存器low_sw由1变为0时,led_ctrl的值变为高,维持一个时钟周期

wire led_ctrl = low_sw_r & ( ~low_sw);

//---------------------------------------------------------------------

endmodule

键盘扫描参照网上的,为了看仿真波形循环写小了点

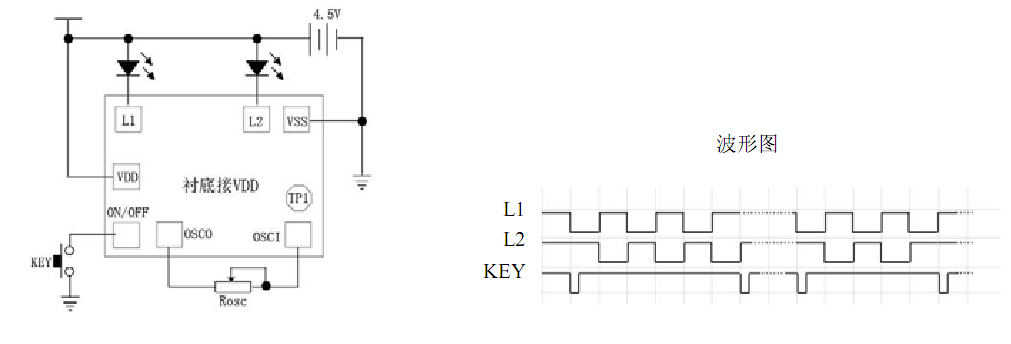

设计要求是这样 (原文件名:QQ截图未命名.png)

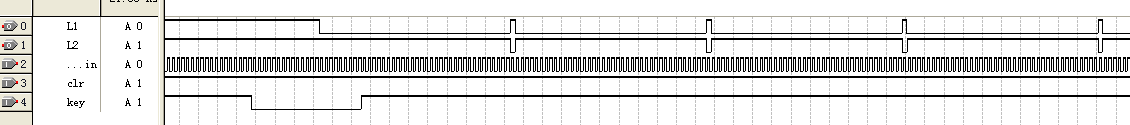

我程序得到的波形,跟要求的为什么不一样 (原文件名:QQ截图未命名是.png) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|