|

|

先说下程序目的:目的是给芯片提供工作信号。

1:时钟信号CKI,由外部60MHZ晶振分频得到10MHZ工作时钟信号,程序中CI_CKI1块还未写,暂且认为CKI=CI_CKI0.

2:DAI,数据输入,在CKI的上升沿会自动读取数据,所以要求在CKI上升沿时保证数据有效。

3:STI信号,在读取48个数据时来一个下降沿,使能输出。

4:POL,SDO都无需考虑。

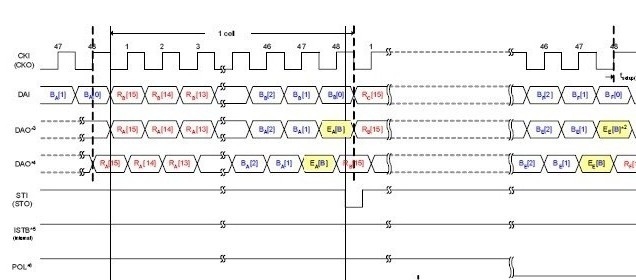

总得来说就是想得到下面的信号:

想要得到的信号 (原文件名:~D{AXAK1YV0[_$U(])UK~OL.jpg)

module dm412(OSC,rest,A0,A1,A2,A3,CKI,STI,DAI,SDO,POL);//A0~A3是电脑输给FPGA的信号。

input OSC,rest,A0,A1,A2,A3;

output CKI,DAI,SDO,POL,STI;

wire SDO;

wire R0,R1,R2,R3,R4,R5,R6,R7;

reg CI_CKI0,CI_CKI1,STI0,CKI,POL,STI;

reg [7:0] T;

reg [7:0] K;

reg [7:0] J;

reg [15:0] DATA;

reg DAI;

/*========Rx用来控制输出一组数据DATA[15:0]===================*/

assign R0=~A3&~A2&~A1&~A0;/*==dianliu ce shi=======0000===*/

assign R1=~A3&~A2&~A1&A0;/*====lou di liu========0001============*/

assign R2=~A3&~A2&A1&~A0;/*========================0010============*/

assign R3=~A3&~A2&A1&A0;/*=========================0011============*/

assign R4=~A3&A2&~A1&~A0;/*========================0100============*/

assign R5=~A3&A2&~A1&A0;/*=========================0101============*/

assign R6=~A3&A2&A1&~A0;/*=========================0110============*/

assign R7=~A3&A2&A1&A0;/*==========================0111============*/

assign R8=A3&~A2&~A1&~A0;/*========================1000============*/

assign R9=A3&~A2&~A1&A0;/*=========================1001============*/

assign R10=A3&~A2&A1&~A0;/*========================1010============*/

assign R11=A3&~A2&A1&A0;/*=========================1011=============*/

assign R12=A3&A2&~A1&~A0;/*========================1100=============*/

assign R13=A3&A2&~A1&A0;/*=========================1101=============*/

assign R14=A3&A2&A1&~A0;/*============PWM==========1110=============*/

assign R15=A3&A2&A1&A0;/*========zi suo cun =======1111=============*/

assign SDO =1'b1;

/*=============分频产生CI_CKI0===============================*/

parameter P=6;

always@(posedge OSC or negedge rest)

if(!rest)

begin

T<=1'b0;

CI_CKI0<=1'b0;

end

else

if(T<P/2-1)

begin

T<=T+1'b1;

end

else

begin

T<=1'b0;

CI_CKI0<=~CI_CKI0;

CKI=(R15)?CI_CKI1:~CI_CKI0;

end

/*================================STI0======================*/

always@(posedge CKI or negedge rest)

if(!rest)

begin

K<=1'b0;

end

else

if(K=='b110000)//========48

begin

K<=1'b0;

end

else

begin

K<=K+1'b1;

end

always@(posedge CKI or negedge rest)

if(!rest)

begin

STI0<=1'b1;

end

else

if(K<='b101111)//=========47

begin

STI0<=1'b1;

end

else

begin

STI0<=1'b0;

end

/*========================DAI==================================*/

always@(posedge OSC or negedge rest)

if(!rest)

begin

J<=1'b0;

end

else

if(J==8'b1100000)//===============96

begin

J<=1'b0;

end

else

begin

J<=J+1'b1;

end

always@(posedge CKI or negedge rest)

if(!rest)

begin

DAI<=1'b0;

STI =(R1)?1'b1:((R15)?1'b1:STI0);

POL=(R14)?1'b0:((R13)?1'b0:1'b1);

/*=========================给DATA[15:0]赋值================*/

DATA[0]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b1

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b0

:((R12)?1'b0

:((R13)?1'b0

:((R14)?1'b0

:1'b1))))))))))))));

DATA[1]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b0

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b0

:((R8)?1'b0

:((R9)?1'b0

:((R10)?1'b1

:((R11)?1'b0

:((R12)?1'b1

:((R13)?1'b1

:((R14)?1'b1

:1'b1))))))))))))));

DATA[2]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b0

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b0

:((R12)?1'b0

:((R13)?1'b0

:((R14)?1'b0

:1'b1))))))))))))));

DATA[3]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b0

:((R4)?1'b1

:((R5)?1'b0

:((R6)?1'b1

:((R7)?1'b0

:((R8)?1'b1

:((R9)?1'b1

:((R10)?1'b1

:((R11)?1'b0

:((R12)?1'b0

:((R13)?1'b0

:((R14)?1'b1

:1'b0))))))))))))));

DATA[4]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b0

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b1

:((R10)?1'b1

:((R11)?1'b0

:((R12)?1'b0

:((R13)?1'b0

:((R14)?1'b0

:1'b0))))))))))))));

DATA[5]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b0

:((R10)?1'b1

:((R11)?1'b1

:((R12)?1'b1

:((R13)?1'b0

:((R14)?1'b1

:1'b0))))))))))))));

DATA[6]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b0

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b0

:((R10)?1'b0

:((R11)?1'b0

:((R12)?1'b1

:((R13)?1'b1

:((R14)?1'b0

:1'b1))))))))))))));

DATA[7]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b1

:((R5)?1'b0

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b1

:1'b0))))))))))))));

DATA[8]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b0

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b1

:((R11)?1'b0

:((R12)?1'b1

:((R13)?1'b0

:((R14)?1'b0

:1'b0))))))))))))));

DATA[9]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b1

:1'b1))))))))))))));

DATA[10]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b0

:1'b1))))))))))))));

DATA[11]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b0

:((R10)?1'b1

:((R11)?1'b0

:((R12)?1'b1

:((R13)?1'b0

:((R14)?1'b1

:1'b0))))))))))))));

DATA[12]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b0

:1'b1))))))))))))));

DATA[13]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b1

:((R5)?1'b0

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b1

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b0

:((R12)?1'b0

:((R13)?1'b0

:((R14)?1'b1

:1'b0))))))))))))));

DATA[14]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b1

:((R3)?1'b1

:((R4)?1'b1

:((R5)?1'b0

:((R6)?1'b0

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b0

:1'b1))))))))))))));

DATA[15]=(R0)?1'b1:((R1)?1'b1

:((R2)?1'b0

:((R3)?1'b1

:((R4)?1'b0

:((R5)?1'b1

:((R6)?1'b1

:((R7)?1'b1

:((R8)?1'b0

:((R9)?1'b1

:((R10)?1'b0

:((R11)?1'b1

:((R12)?1'b0

:((R13)?1'b1

:((R14)?1'b1

:1'b1))))))))))))));

end

/*===========在CKI上升沿之前给数据,保证读取数据时数据维持一定时间==============*/

else if (J<=8'd1) begin DAI<=DATA[0];end

else if (J<=8'd7) begin DAI<=DATA[1];end

else if (J<=8'd13) begin DAI<=DATA[2];end

else if (J<=8'd19) begin DAI<=DATA[3];end

else if (J<=8'd25) begin DAI<=DATA[4];end

else if (J<=8'd31) begin DAI<=DATA[5];end

else if (J<=8'd37) begin DAI<=DATA[6];end

else if (J<=8'd43) begin DAI<=DATA[7];end

else if (J<=8'd49) begin DAI<=DATA[8];end

else if (J<=8'd55) begin DAI<=DATA[9];end

else if (J<=8'd61) begin DAI<=DATA[10];end

else if (J<=8'd67) begin DAI<=DATA[11];end

else if (J<=8'd73) begin DAI<=DATA[12];end

else if (J<=8'd85) begin DAI<=DATA[14];end

else if (J<=8'd79) begin DAI<=DATA[13];end

else if (J<=8'd91) begin DAI<=DATA[15];end

end

endmodule

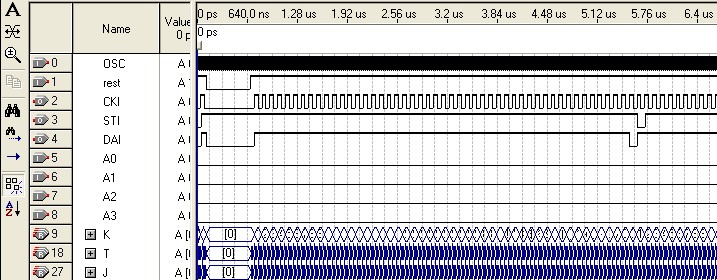

现在数据输出部分很有问题:

(原文件名:VO$4[TH5OREO[X$P8V$EEYH.jpg)

这是我A0~A3全给0,即R0有效,DAI应该输出全1,但是DAI怎么有个低位呢,给其他数据也都有问题。

初学者,程序很繁琐, 海涵。。。。。。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|