|

|

module fillzero(datain,inEn,reset,CLK_I,CLK_O,dataout,fill_rdy);

input datain;

input inEn; //

input reset;

input CLK_I;

input CLK_O;

output dataout;

output fill_rdy;

reg BUF2_RDY;

reg [2:0] i;

reg [2:0] j;

//reg [3:0] BUF1;

reg [5:0] BUF2;

reg dataout;

reg fill_rdy;

/*always @ ( negedge reset or posedge CLK_I )

begin

if ( ! reset )

begin

BUF1 <= 0;

i <= 0;

end

else

begin

if ( inEn )

begin

case (i)

2'b00:

begin

BUF1[0] <= datain;

BUF1_RDY <= 1;

i <= i + 1 ;

end

2'b01:

begin

BUF1[1] <= datain;

BUF1_RDY <= 1;

i <= i + 1 ;

end

2'b10:

begin

BUF1[2] <= datain;

BUF1_RDY <= 1;

i <= i + 1 ;

end

2'b11:

begin

BUF1[3] <= datain;

BUF1_RDY <= 1;

i <= 2'b00 ;

end

default:

begin

BUF1 <= 0;

BUF1_RDY <= 0;

i <= 0;

end

endcase

end

else

begin

BUF1_RDY <= 0;

BUF1 <= 0;

i <= 0;

end

end

end */

always @ ( negedge reset or posedge CLK_I )

begin

if ( ! reset )

begin

BUF2<=0;

j <= 3'b000;

BUF2_RDY<=0;

end

else if ( inEn )

begin

case (j)

3'b000,3'b001,3'b010:

begin

BUF2[j] <= datain;

BUF2_RDY <= 1;

j <= j + 1 ;

end

3'b011:

begin

BUF2[j]<= 1'b0;

BUF2[j+1]<= 1'b0;

BUF2[j+2]<= datain ;

BUF2_RDY <= 1;

j <= 3'b000 ;

end

default:

begin

BUF2 <= 0;

BUF2_RDY <= 0;

j <= 3'b000;

end

endcase

end

else

begin

BUF2 <= 0;

BUF2_RDY <= 0;

j <= 3'b000;

end

end

always @ ( negedge reset or posedge CLK_O )

begin

if ( ! reset )

begin

dataout<=0;

fill_rdy<=0;

i <= 3'b000;

end

else if ( BUF2_RDY )

begin

case (i)

3'b000,3'b001,3'b010,3'b011,3'b100:

begin

dataout <= BUF2;

fill_rdy<= 1;

i <= i + 1 ;

end

3'b101:

begin

dataout<=BUF2;

fill_rdy<=1;

i <= 3'b000 ;

end

default:

begin

dataout <= 0;

fill_rdy <= 0;

i <= 3'b000;

end

endcase

end

else

begin

dataout <= 0;

fill_rdy <= 0;

end

end

endmodule

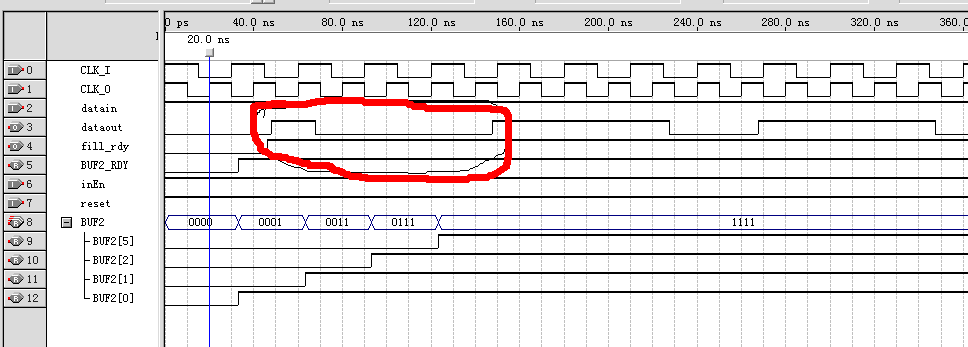

下面是截图,第三幅图红笔圈的地方不对。

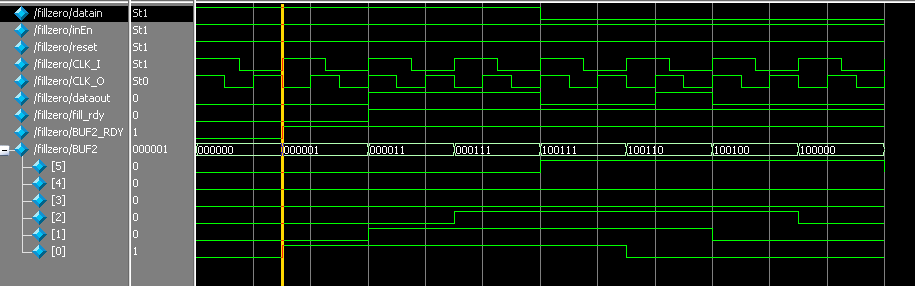

功能仿真图 (原文件名:QQ截图未命名1.png)

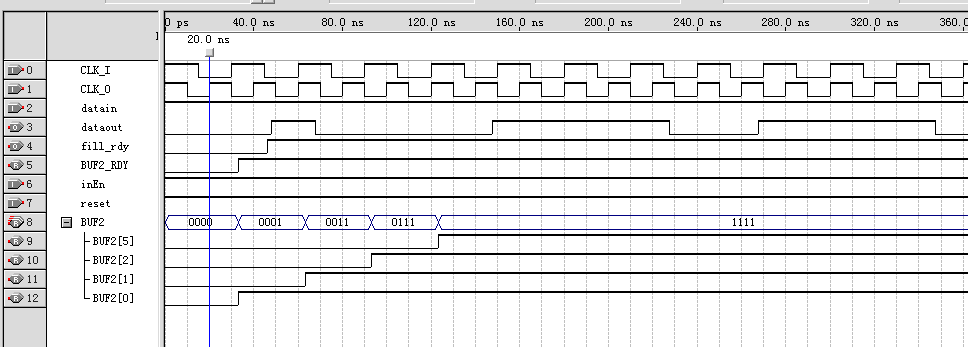

时序仿真图 (原文件名:QQ截图未命名2.png)

红笔圈出的地方不对 (原文件名:QQ截图未命名22.PNG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|