|

|

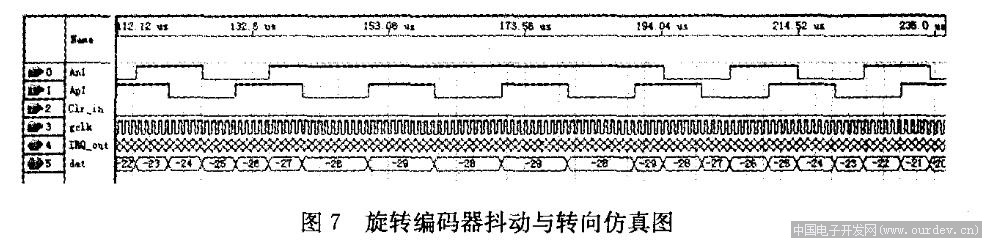

我是要做一个编码器的解码电路,如下图的样子:

需要在每个A相和B相的跳变沿,改变计数器的值。

(原文件名:未命名.JPG)

编写了2个UDP来检测AB的跳变,后面的module里面将跳变信号转化为计数器加减值,但是发现程序下载到片子里面不能用啊,计数器的加减值不变的~~~~求助大虾看看是咋回事呢~~

//正转时,由AB相每个沿产生正向的跳变

primitive F_pulse(f_en,ain,bin,reset);

output f_en;

reg f_en;

input ain, bin,reset;

initial begin

f_en=0;

end

table

// ain bin reset: f_en_state : f_en_next

p 0 ? : ? : 1;

n 1 ? : ? : 1;

1 p ? : ? : 1;

0 n ? : ? : 1;

? ? n : ? : 0;

? ? ? : ? : -;

endtable

endprimitive

//反转时,由AB相每个沿产生正向的跳变

primitive R_pulse(r_en,ain,bin,reset);

output r_en;

reg r_en;

input ain, bin,reset;

initial begin

r_en=0;

end

table

// ain bin reset: r_en_state : r_en_next

p 1 ? : ? : 1;

n 0 ? : ? : 1;

0 p ? : ? : 1;

1 n ? : ? : 1;

? ? n : ? : 0;

? ? ? : ? : -;

endtable

endprimitive |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|