|

|

请各位大牛帮忙分析下,我在做一个数字电压表,现在从ADC0809中输出的数字量不稳定,我觉得是干扰造成的,但是不知道怎么去排除干扰,请问有哪些方法去检查调试啊?另外数字量输入到FPGA中,会不会是FPGA控制的问题呢?另外我用的FPGA扩展接口是3.3V是否需要转换到5V呀?

电路方面除了5V直流电源和ADC0809电路就没其他的电路了,从ADC0809输出的数字量就输入FPGA了,而正是这个地方不稳定,在示波器上看这个输出8位都有杂波,而且干扰还挺大的。

我举个例子吧。输出为abcdefgh<=01000000为正确的 而输出数字量不稳定b在0,1间跳变 即00000000,01000000。除了全1和全0是稳定的,其他的都不稳定。

下面先给出FPGA控制ADC0809工作的代码

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity ADC0809 is

Port ( CLK0 : in STD_LOGIC;----------------------------50Mhz板级输入时钟

EOC0 : in STD_LOGIC;----------------------------转换信号

D0 : in STD_LOGIC_VECTOR (7 downto 0);-------来自0809转换好的数据

q0 : inout STD_LOGIC_VECTOR (7 downto 0);-------实际8位数字量数据信号

CLK500KHZ0 : out STD_LOGIC;---------------------500Khz时钟

ALE0 : out STD_LOGIC;---------------------------8个模拟信号通道地址锁存信号

START0 : out STD_LOGIC;-------------------------转换开始信号

OE0 : out STD_LOGIC);----------------------------数据输出三态控制

end ADC0809;

architecture Behavioral of ADC0809 is

signal clk_div : std_logic;----------------分频所得500Khz时钟用于驱动AD0809

TYPE states IS (idle,start_h,transition,out_data,latch);---------------

----------五个状态分别对应初始化,启动采样,转换,输出数据,锁存-----------

signal current_state,next_state : states:=idle;----状态初始化

signal qq : std_logic_vector(7 downto 0);

signal lock0 : std_logic;

begin

q0<=qq;

--------------------分频模块--------------------

process(CLK0)

variable clk_cnt:integer range 100 downto 0;

begin

if (CLK0'event and CLK0='1') then

if clk_cnt=50 then clk_div<=not clk_div;

clk_cnt:=0;

else clk_cnt:=clk_cnt+1;

end if;

end if;

end process;

CLK500KHZ0<=clk_div;

--------------------分频模块--------------------

-----------------AD0809控制模块----------------

com1:process(current_state,EOC0)--------组合进程

begin

case current_state is

when idle => next_state<=start_h;

when start_h => next_state<=transition;

when transition => if(EOC0='1') then next_state<=out_data;

else next_state<=transition;

end if;

when out_data => next_state<=latch;

when latch => next_state<=idle;

when others => next_state<=idle;

end case;

end process;

com2:process (current_state)--------组合进程

begin

case current_state is

when idle => ALE0<='0';START0<='0';OE0<='0';lock0<='0';

when start_h => ALE0<='1';START0<='1';OE0<='0';lock0<='0';

when transition => ALE0<='0';START0<='0';OE0<='0';lock0<='0';

when out_data => ALE0<='0';START0<='0';OE0<='1';lock0<='0';

when latch => ALE0<='0';START0<='0';OE0<='1';lock0<='1';

when others =>ALE0<='0';START0<='0';OE0<='0';lock0<='0';

end case;

end process;

reg:process (clk_div)---------------时序进程

begin

if (clk_div'event and clk_div='1') then current_state<=next_state;

end if;

end process;

latch1:process (lock0)--------锁存进程

begin

if (lock0'event and lock0='1') then qq<=D0;

end if;

end process;

-----------------AD0809控制模块-----------------

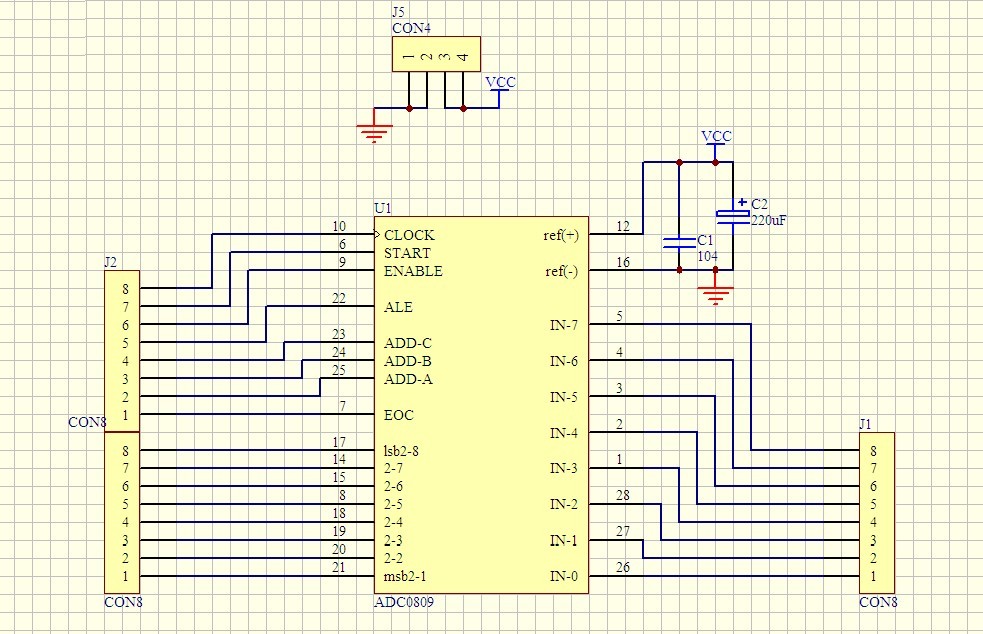

下面附上ADC0809的原理图

(原文件名:原理图.jpg)

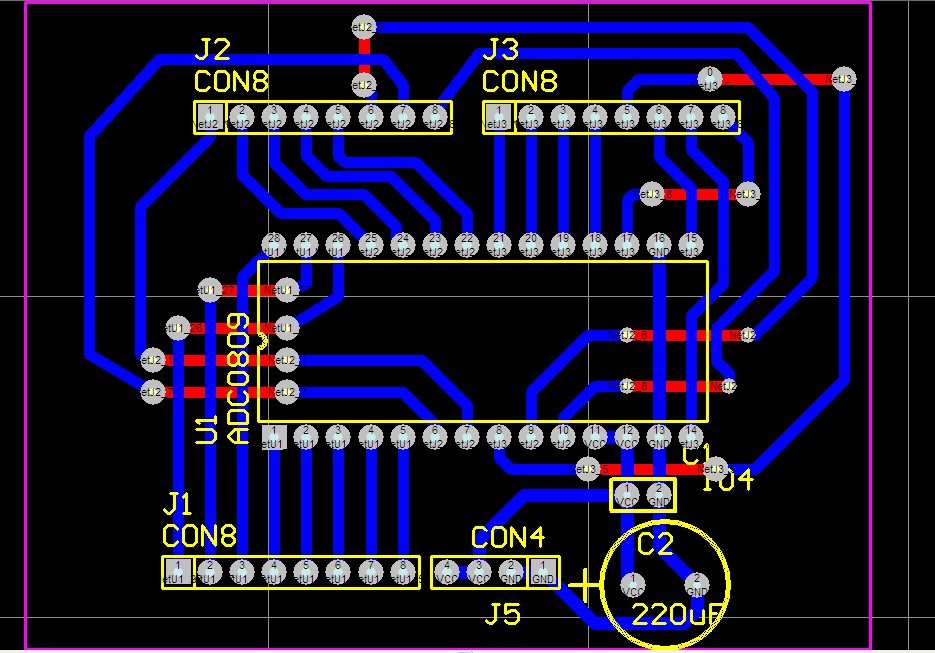

下面是ADC0809的PCB图

(原文件名:pcb图.jpg)

小弟在此先谢了啊!希望各位大牛能多提些调试检查方法。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|