|

|

(原文件名:未命名.JPG)

////////////////////////////////////////////////////////////////

源代码如下:

module flash2(

input clk,

input write, //写请求

input rst, //上电复位

output reg we_n

);

parameter Trhr=6; //Trhr最少要保持50ns的高电平,这里保持的时间是60ns

parameter Trp=5;

parameter Tas=2; //地址建立时间为20ns

parameter Tah=6; //地址保持时间至少30ns,这里用的是60ns

parameter Twph=4; //写脉冲高电平宽度最小要30ns这里用的是40ns

parameter Twp=4;

reg [4:0] cs,ns;

parameter clr=3'b000;

parameter idle=3'b010;

parameter wr0=3'b011; //写第一个指令

parameter wr1=3'b100;//写第二个指令

parameter wr2=3'b101;//写第三个指令

parameter wr3=3'b110;//写数据

always @ (posedge clk or negedge rst)

if(!rst) //上电复位,片清除

cs<=clr;

else

cs<=ns;

always @ (cs or rst_cnt or write

or wr_cnt)

case(cs)

clr:begin

if(rst_cnt==Trp)

ns=idle;

else

ns=clr;

end

idle:begin

if(write) //写请求

ns=wr0;

else

ns=idle;

end

wr0:begin

if(wr_cnt==Tas+Tah-1)

ns=wr1;

else

ns=wr0;

end

wr1:begin

if(wr_cnt==Tas+Tah-1)

ns=wr2;

else

ns=wr1;

end

wr2:begin

if(wr_cnt==Tas+Tah-1)

ns=wr3;

else

ns=wr2;

end

wr3:begin

if(wr_cnt==Tas+Tah-1)

ns=idle;

else

ns=wr3;

end

default:begin

ns=idle;

end

endcase

always @(cs or wr_cnt)

case(cs)

clr:we_n<=1'b1;

idle:we_n<=1'b1;

wr0:begin

if(wr_cnt>=Tas&&wr_cnt<(Tas+Twp))//建立时间到

we_n<=1'b0;//写使能拉低

else if(wr_cnt>=(Tas+Twp))//保持时间到

we_n<=1'b1; //写使能拉高

else

we_n<=1'b1;

end

wr1:begin

if(wr_cnt>=Tas&&wr_cnt<(Tas+Twp)) //建立时间到

we_n<=1'b0;//写使能拉低

else if(wr_cnt>=(Tas+Twp))//保持时间到

we_n<=1'b1; //写使能拉高

else

we_n<=1'b1;

end

wr2:begin

if(wr_cnt>=Tas&&wr_cnt<(Tas+Twp)) //建立时间到

we_n<=1'b0;//写使能拉低

else if(wr_cnt>=(Tas+Twp))//保持时间到

we_n<=1'b1; //写使能拉高

else

we_n<=1'b1;

end

wr3:begin

if(wr_cnt>=Tas&&wr_cnt<(Tas+Twp)) //建立时间到

we_n<=1'b0;//写使能拉低

else if(wr_cnt>=(Tas+Twp))//保持时间到

we_n<=1'b1; //写使能拉高

else

we_n<=1'b1;

end

default:begin

we_n<=1'b1;

end

endcase

reg [5:0] rst_cnt;

reg [3:0] wr_cnt;

always @ (posedge clk or negedge rst)

if(!rst)

begin

rst_cnt<=5'd0;

wr_cnt<=3'd0;

end

else

begin

if(cs==clr)

rst_cnt<=rst_cnt+1'b1;

else

rst_cnt<=5'd0;

if(cs==wr0||cs==wr1 || cs==wr2 ||cs==wr3)

if(wr_cnt==4'd8)

wr_cnt<=4'd0;

else

wr_cnt<=wr_cnt+1'b1;

end

endmodule

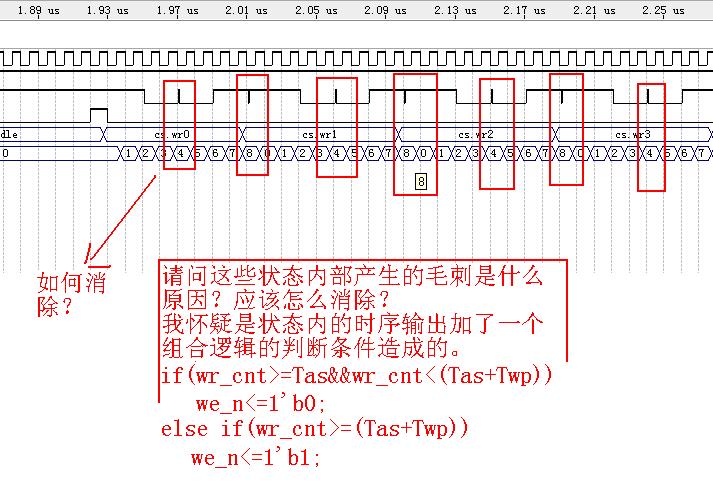

设计flash的驱动电路的时候需要用到这个时序,但是在设计的时候发现在状态内部输出的时候会有毛刺,而这些毛刺都很有规律,我怀疑是设计的问题,

应该是组合时序输出用到了组合逻辑判断造成的,请问具体是什么原因?该如何消除,设计类似的时序的时候一般用什么方法?谢谢大家.

点击此处下载 ourdev_572045.rar(文件大小:266K) (原文件名:tst.rar) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|