|

|

小弟在看一篇关于时序约束的文章(下面的内容)时碰到个问题:Tclk_skew取值正或负,好像与“开发中器件”的状态(处于输入数据或输出数据)有关,各位大牛帮帮忙,能详细解释下嘛?(为什么在E中Tclk_skew满足时序关系为负?而在G中Tclk_skew满足时序关系为正?)

E 关于输入到达时间

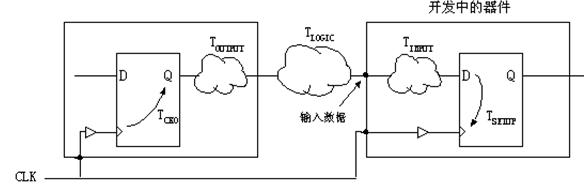

Xilinx的"输入到达时间的计算"时序描述如下图所示:

(原文件名:2PU6153531.jpg)

图2 输入到达时间示意图

定义的含义是输入数据在有效时钟沿之后的TARRIVAL时刻到达。则,

TARRIVAL=TCKO+TOUTPUT+TLOGIC 公式1

根据上面介绍的周期(Period)公式,我们可以得到:

Tcko+Toutput+Tlogic+Tinput+Tsetup-Tclk_skew=Tclk; 公式2

将公式1代入公式2: Tarrival+Tinput+Tsetup-Tclk_skew=Tclk, 而Tclk_skew满足时序关系后为负,所以

TARRIVAL +TINPUT+TSETUP <TCLK 公式3

这就是Tarrival应该满足的时序关系。其中TINPUT为输入端的组合逻辑、网线和PAD的延迟之和,TSETUP为输入同步元件的建立时间。

G 要求输出的稳定时间

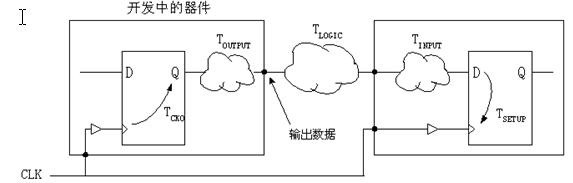

从下一级输入端的延迟可以计算出当前设计输出的数据必须在何时稳定下来,根据这个数据对设计输出端的逻辑布线进行约束,以满足下一级的建立时间要求,保证下一级采样的数据是稳定的。计算要求的输出稳定时间如下图所示:

(原文件名:2PUZc450.jpg)

图4 要求的输出稳定时间示意图

公式的推导如下:

定义:TSTABLE = TLOGIC +TINPUT +TSETUP

从前面帖子介绍的周期(Period)公式,可以得到(其中TCLK_SKEW=TCLK1-TCLK2):

TCLK=TCKO+TOUTPUT+TLOGIC+TINPUT+TSETUP+TCLK_SKEW

将TSTABLE的定义代入到周期公式,可以得到:

TCLK=TCKO+TOUTPUT+TSTABLE+TCLK_SKEW

所以:TCKO +TOUTPUT+TSTABLE<TCLK

这个公式就是TSTABLE必须要满足的基本时序关系,即本级的输出应该保持怎么样的稳定状态,才能保证下级芯片的采样稳定。有时我们也称这个约束关系是输出数据的保持时间的时序约束关系。只要满足上述关系,当前芯片输出端的数据比时钟上升沿提早TSTABLE 时间稳定下来,下一级就可以正确地采样数据。其中TOUTPUT为设计中连接同步元件输出端的组合逻辑、网线和PAD的延迟之和,TCKO为同步元件时钟输出时间。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|