|

|

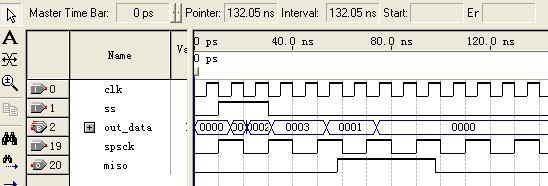

现在是ss为高电平时取计数数据,低电平时SPI发送,仿真通过但总觉得有点别扭

请教如何改?才能达到只在ss的下降沿才执行一次读取计数器的动作。

/* SPI SLAVE */

module Clock(clk,spsck,mosi,miso,ss);

input clk,spsck,mosi,ss;

output miso;

reg [15:0] counter;

reg [15:0] out_data;

reg miso;

always@(posedge clk)

begin

counter = counter+1;

end

always@(posedge spsck or posedge ss)

begin

if (ss)

begin

out_data = counter; // 如何改?才能使此句只在ss的下降沿才执行一次

end

else

begin

miso = out_data[0];

out_data = out_data >> 1;

end

end

endmodule

仿真波形 (原文件名:simclock.JPG)

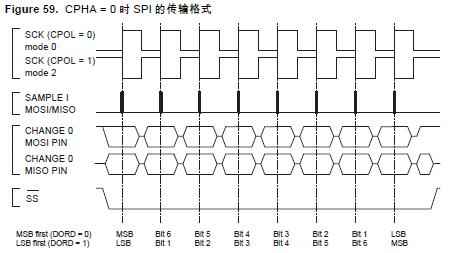

SPI时序 (原文件名:m8spi.JPG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|