|

|

我最近在做roasn的逻辑分析仪方案,但是FPGA换成了altera公司的EP1C6T144C8,具有两个锁相环PLL,5980个LE,20个M4K RAM,最大用户可使用I/O 98个。

现在的问题是,USB固件烧写没什么问题。但是在便宜FPGA程序时,出现了时序紧张的问题。

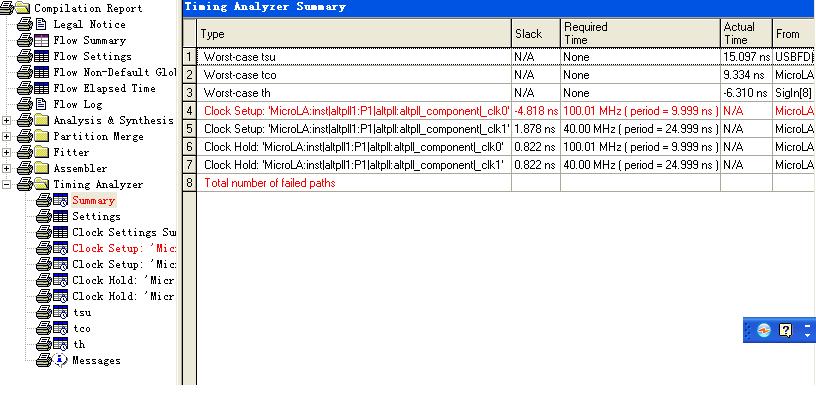

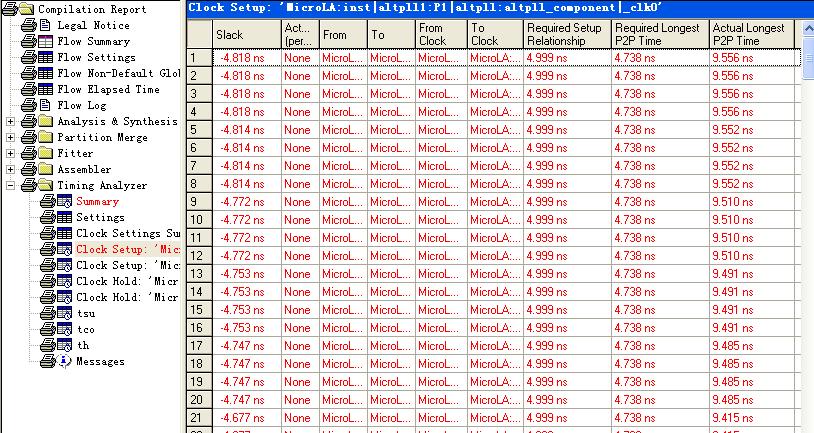

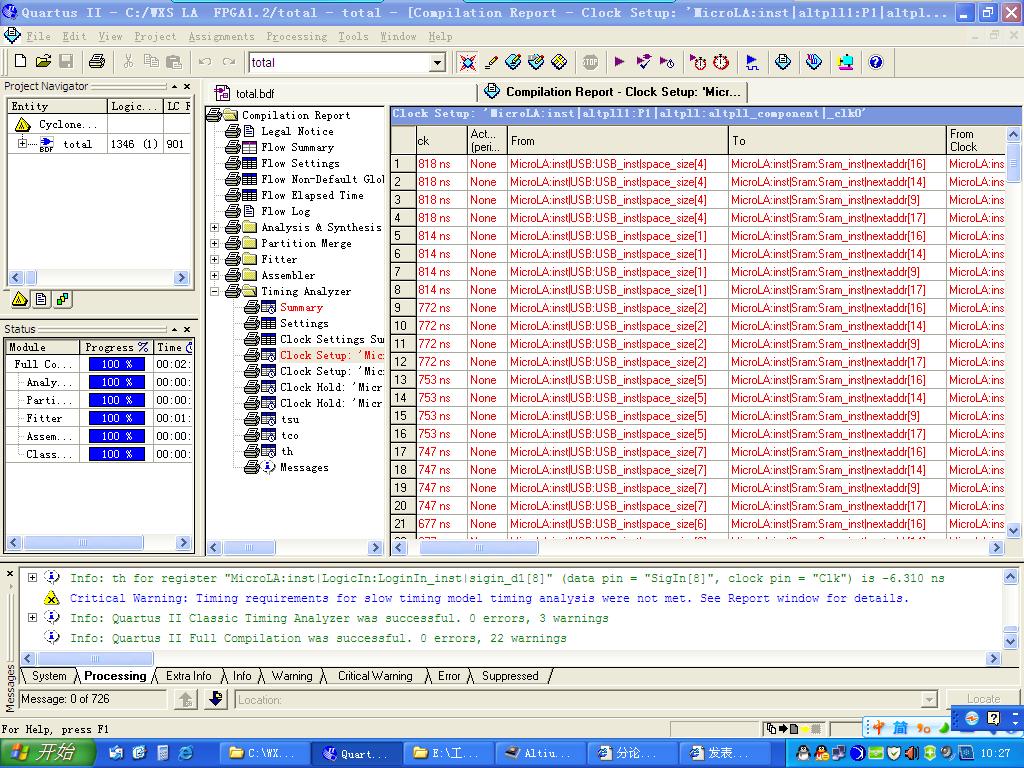

程序改动:在roasn程序基础上,去掉DCM,改用PLL。另外,FPGA系统输入时钟为24MHz,用PLL倍频至100MHz后,送给sram单元(100M晶振有点贵,就用片上资源了)。下面是仿真结果,发现slack为负值了,这样的结果,可能造成系统不稳定,就是说可能在常温情况下,系统工作没问题,但是环境温度升高一点,或者长时间工作后,系统就会失控了:

(原文件名:时序1.JPG)

(原文件名:时序2.JPG)

(原文件名:时序3.JPG)

疑问:按照以往工程经验,PLL输出时钟是非常标准的,在pll的100M时钟驱动下,后面的USB和SRAM逻辑出现了时序紧张的现象,就我个人的思路看来,觉得像是后面的SRAM操作逻辑有问题,因为除pll逻辑外,其它部分我都没有变动。而pll只是单纯的提供100M时钟而已,且是标准时钟,也不太可能有什么问题啊。

我记得网站上有个朋友用altera的EP1C6Q240也做过rosan的方案,不知碰到过这种问题没有?另外roasn朋友做仿真的时候,将CLK时钟提高至100M,是否会出现这种现象呢?

以上是自己一点不程序的想法,如果有不妥之处,请见谅! |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|