|

|

按照duoduo(在此表示由衷的感谢)的《CPLD/FPGA中双向总线的实现方法》中的程序,如下:

/*****************************************/

module BiBus(hwr_,hrd_,hd,swr_,srd_,sd);

input hwr_;

input hrd_;

inout [7:0] hd;

output swr_;

output srd_;

inout [7:0] sd;

/*****************************************/

wire hd_out_oe;

reg [7:0] hd_out;

wire sd_out_oe;

reg [7:0] sd_out;

/*****************************************/

always @(hwr_) begin

if(!hwr_) sd_out=hd;

end

/*****************************************/

always @(hrd_) begin

if (!hrd_) hd_out=sd;

end

/*****************************************/

assign swr_=hwr_;

assign srd_=hrd_;

assign sd_out_oe=!hwr_;

assign hd_out_oe=!hrd_;

assign hd=hd_out_oe?hd_out:8'hzz;

assign sd=sd_out_oe?sd_out:8'hzz;

/*****************************************/

endmodule

/*****************************************/

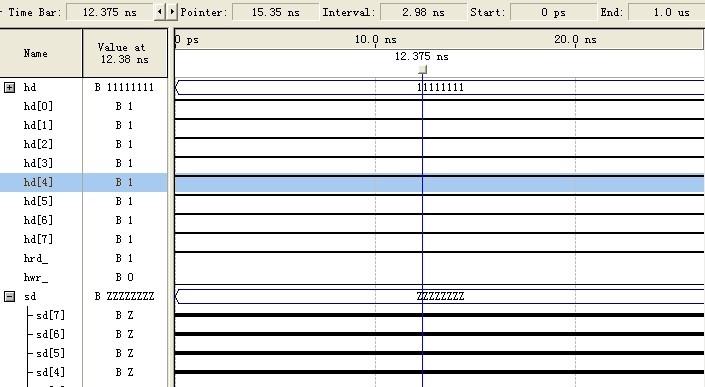

设计双向总线,为什么仿真总不对,波形如下:

(原文件名:1.jpg)

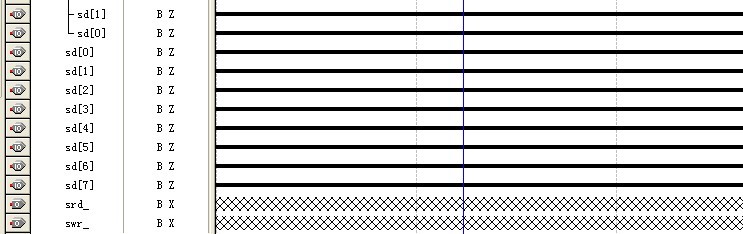

(原文件名:2.jpg)

仿真时设置为写信号为低,读信号为高,应该是sd=hd才对啊,仿真时已把hd值为11111111了,为什么输出的sd为高阻状态,而且swr_和srd_的状态也不对,高手指教。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|