|

|

发表于 2010-3-15 21:09:44

|

显示全部楼层

发表于 2010-3-15 21:09:44

|

显示全部楼层

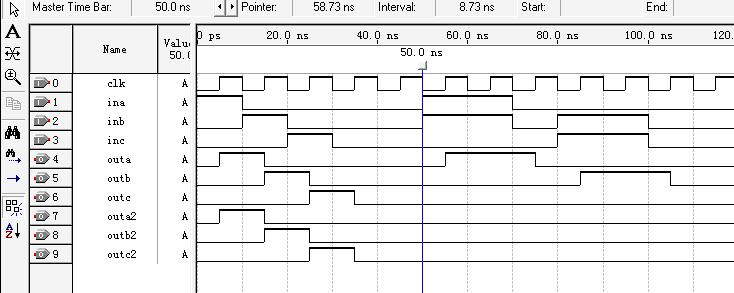

好像不对,a=b=1的时候只会执行if(a)后面的那个语句。

我做过实验的,你看嘛。基本上照着你写的。

module test (clk,ina,inb,inc,outa,outb,outc,outa2,outb2,outc2);

input clk,ina,inb,inc;

output outa,outb,outc,outa2,outb2,outc2;

reg outa,outb,outc,outa2,outb2,outc2;

always @ (posedge clk)

if(ina==1'b1)

begin

outa<=1'b1;

outb<=1'b0;

outc<=1'b0;

end

else if(inb==1'b1)

begin

outa<=1'b0;

outb<=1'b1;

outc<=1'b0;

end

else if(inc==1'b1)

begin

outa<=1'b0;

outb<=1'b0;

outc<=1'b1;

end

else

begin

outa<=1'b0;

outb<=1'b0;

outc<=1'b0;

end

always @ (posedge clk)

case({ina,inb,inc})

3'b100:begin

outa2<=1'b1;

outb2<=1'b0;

outc2<=1'b0;

end

3'b010:begin

outa2<=1'b0;

outb2<=1'b1;

outc2<=1'b0;

end

3'b001:begin

outa2<=1'b0;

outb2<=1'b0;

outc2<=1'b1;

end

default :begin

outa2<=1'b0;

outb2<=1'b0;

outc2<=1'b0;

end

endcase

endmodule

(原文件名:未命名.JPG) |

|