|

|

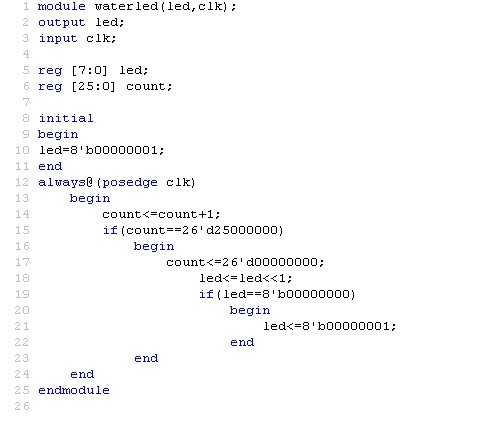

我是一个fpga的小小小菜鸟,刚开始学习,写了一个流水灯的程序,可以运行如下:

(原文件名:1.jpg)

但是看了艾米的例程,如下:

module ledwater(clk,led);

output [7:0] led;

input clk;

reg[8:0] led_out;

reg[8:0] led_out1;

reg[25:0]buffer;

always@(posedge clk)

begin

buffer<=buffer+1'b1;

if (buffer==26'd25000000)

begin

led_out=led_out<<1;

if(led_out==9'b000000000)

led_out=9'b111111111;

led_out1=~led_out;

end

end

assign led=led_out1[7:0];

endmodule

有好多地方的编程风格都不一样。。。。我知道从入门起养成一个良好的编程风格是很重要的,所以请大家尽可能的指正我。。。不要留面子,谢谢。。。。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|