|

|

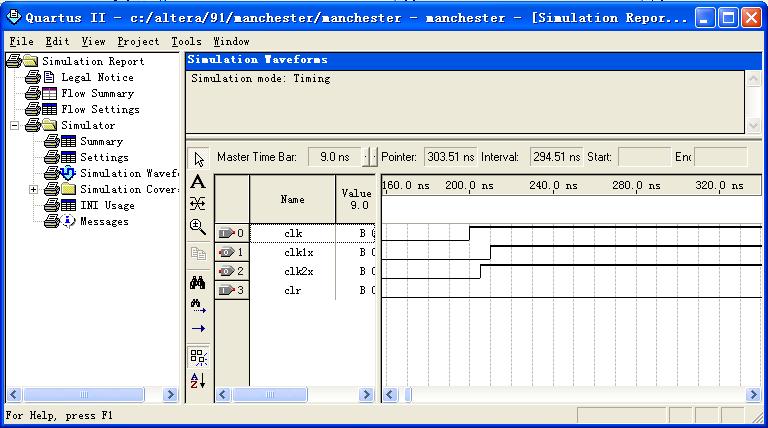

以下vhdl代码实现对CLK 一分频(CLK1X)、二分频(CLK2X)功能,器件型号为EPM7128STC100-10,仿真的结果是CLK1X比CLK2X输出延时整整大一倍(5ns,10ns)

请问要怎么改才能让CLK1X、CLK2X上升沿对齐?

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity manchester is

port(clk,clr:in std_logic;

clk1x,clk2x:out std_logic);

end manchester;

architecture manchecode of manchester is

signal count2:std_logic_vector(1 downto 0);

begin

p1:process(clk)

begin

if(clk'event and clk='1') then

if(clr='1' or count2="11") then

count2<="00";

else

count2<=count2+"01";

end if;

end if;

end process;

clk1x<=clk;

clk2x<=count2(0);

end manchecode;

分频器仿真波形 (原文件名:wave.JPG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|