|

|

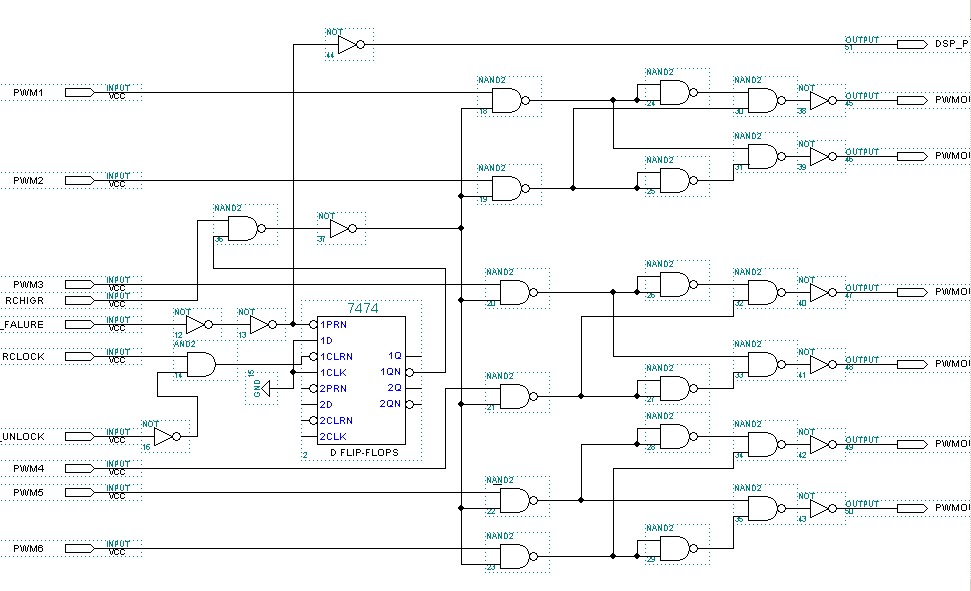

呵呵~ 大家别骂我,其实是个很简单的错误程序,(我只学了一个周,属于超级菜鸟)程序如下: 其实就是为了将下面的原理图用

VERILOG写出来: 可怎么编译就是不过。

module pv1(po1,po2,po3,po4,po5,po6,DSP_PDPINTA,

p1,p2,p3,p4,p5,p6,RCHIGH,IO_FALURE,RCLOCK,IO_UNLOCK);

output po1,po2,po3,po4,po5,po6,DSP_PDPINTA;

input p1,p2,p3,p4,p5,p6,RCHIGH,IO_FALURE,RCLOCK,IO_UNLOCK;

reg po1,po2,po3,po4,po5,po6;

always@(p1 or p2 or p3 or p4 or p5 or p6 or RCHIGH or IO_FALURE or RCLOCK or IO_UNLOCK)

if(!RCHIGH||IO_FALURE||RCLOCK||IO_UNLOCK)

po1<=0;

po2<=0;

po3<=0;

po4<=0;

po5<=0;

po6<=0;

else

po1<=p1;

po2<=p2;

po3<=p3;

po4<=p4;

po5<=p5;

po6<=p6;

else if(p1 xnor p2)

p1<=0;

p2<=0;

else po1<=p1;

po2<=p2;

if(p3 xnor p4)

p3<=0;

p4<=0;

else po3<=p3;

po4<=p4;

if(p5 xnor p6)

p5<=0;

p6<=0;

else po5<=p5;

po6<=p6;

if(!IO_FALURE)

DSP_PDPINTA<=1;

else DSP_PDPINTA<=0;

endmodule

原理图如下: 还望高手不吝指点。。。。

(原文件名:3.jpg) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|