|

|

整理电脑的时候忽然发现当时在学校电子设计时候做过的一个示波器题目的文档。

是用FPGA做的,后来3天的时间太紧了没调出来液晶显示,只用2个通道输出接到示波器上显示....不过功能跟性能要求倒是达到了题目要求甚至扩展要求

贴出一些内容缅怀一下,也供大家参考——如果还有点参考价值的话 >.< 本人认为这是个失败的作品

--------------------------------------------------------------------------------------------------------

数字示波器按照题目要求能做到两种基本的数字化采样模式:等效采样和实时采样。

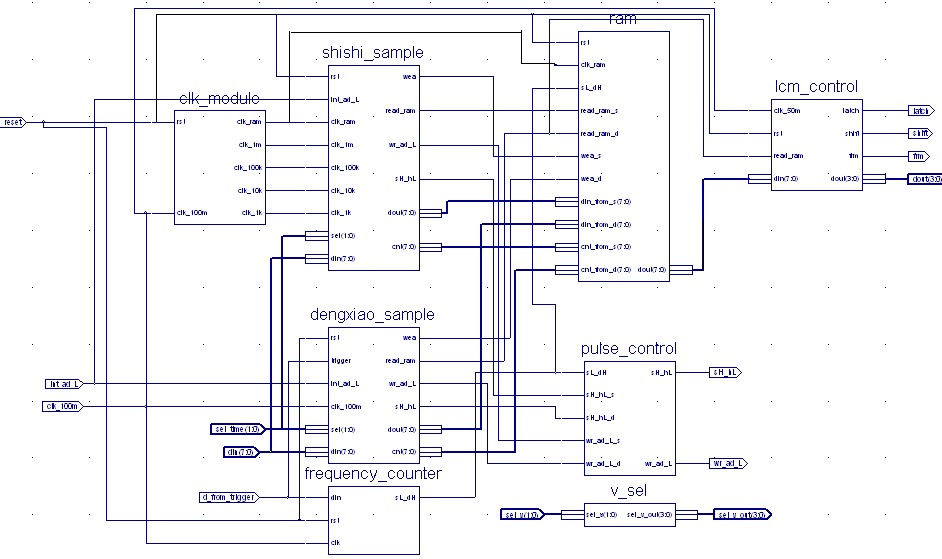

本方案采用高速大规模FPGA芯片实现的高速数据采集控制和存储、垂直通道量程控制、显示控制、时间扩展控制以及其他的外围电路控制,使系统结构大大简化,提高了整体可靠性,同时降低了实现成本。

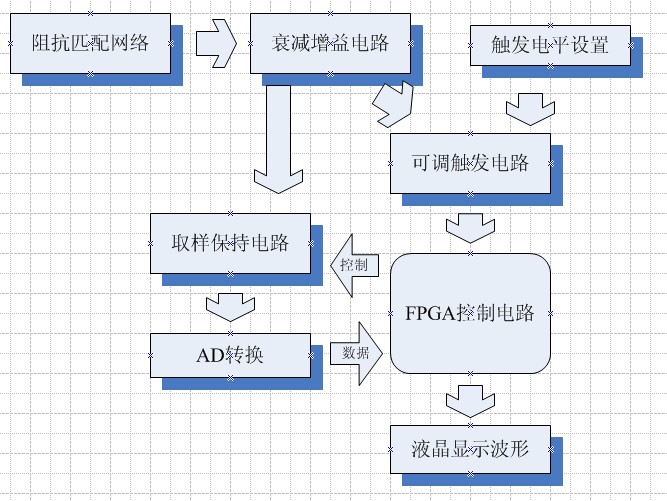

方案流程如图一所示,首先输入的信号经过阻抗匹配电路后进入衰减增益电路进行一定的衰减或者增益处理,使输入信号符合处理的电压范围。接着输入可调增益芯片进行第二次处理,可调增益放大器根据用户选择的档位对信号进行一定的衰减增益后送入采样保持放大器,由FPGA控制采样保持放大器采集并将数据送入ADC芯片,最后ADC芯片处理完的数据被送往FPGA进行最后处理后控制LCM模块将波形和频率、幅值等数据显示到液晶显示屏上。

(原文件名:未命名.jpg)

数字示波器的制作和设计

1. 高阻衰减网络

由于数字工作芯片工作电压较小,不能满足大范围电压信号输入,所以需要设计一高阻衰减器(一般为1MΩ)提供电压衰减,增大测量范围。这里我们选择1/10和1/1衰减电路。当测量较大电压时,进行衰减;输入电压较小时可以选择另一网络直接选通不进行衰减。衰减网络的选择根据用户拨的档位进行切换。能完成基本要求里的垂直灵敏度1V/div和0.1v/div的两档选择和1M欧姆阻抗的基本要求。

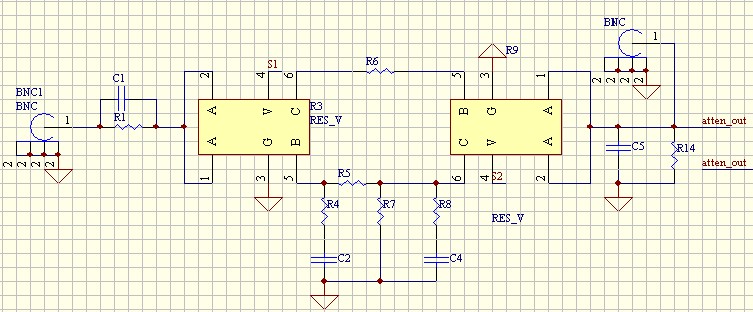

为了产生10:1的衰减,我们采用了如图3所示的电路。该电路由2个74HC4066、2个继电器以及一些容阻组成。RL1和RL2这2个继电器用来选择支路。上面的支路2是无衰减支路,下面的是支路1是10:1衰减。支路的选择由用户拨动档位对继电器的开关进行选择而达到。

(原文件名:1.jpg)

2. 增益衰减电路

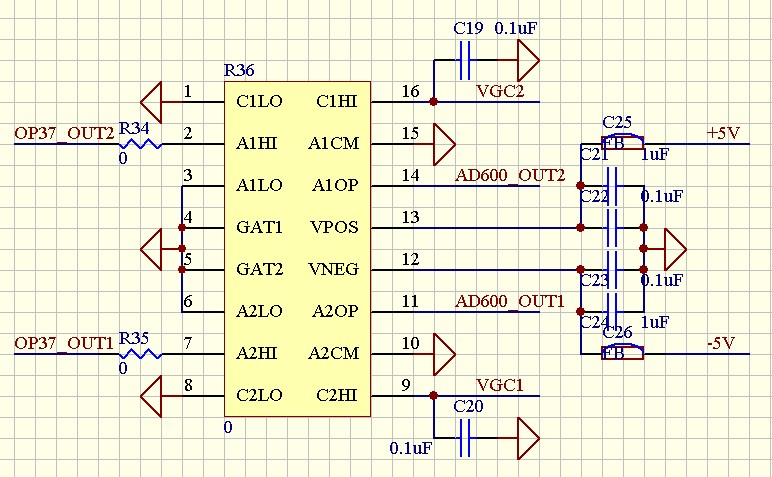

通过4066多路模拟开关控制继电器选择电压档通路,将设定好的参考电压传至可变增益放大器AD600,可以有效的实现多档电压放大,而且电路简单,增益调节简单,精确。每个独立的通道都提供了0-40 db 的增益。

AD600的增益可以按如下公式计算出来(Vg单位是V):Gain (dB) = 32 VG + 20

由于要实现发挥部分的2mv/div档,可以使用AD600根据输入电压的不同对输入信号进行不同增益的方法后给后面的数字电路处理。在输入为垂直灵敏度1V/div和0.1v/div的两档时,AD600增益为2倍,在2mv/div档时则为100倍,由增益公式计算出输入VG分别为0.66V和-0.56V。使用电阻分压电路和继电器对输入电压进行控制,根据用户选择的档位分别输入对应的VG就能控制相应的通道增益。实现3档垂直灵敏度可调。

(原文件名:2.jpg)

3. 比较触发电路和采样电路

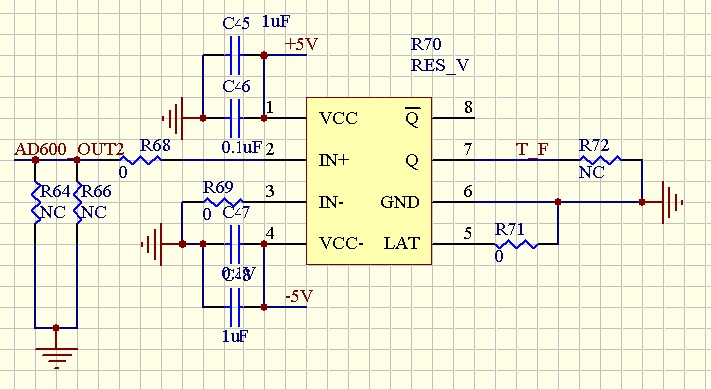

使用高速比较器TL3016经过AD600进行增益衰减后的信号与设置的触发电平进行比较,输出与信号同频的触发脉冲串到FPGA,让FPGA处理后控制AD783采样。

触发电平由可调电阻和固定电阻分压得到,可以3到0V内可调。当输入信号电平高于比较电平时比较器就输出高电平,否则为低电平,能完成基本要求中的触发电平可调。

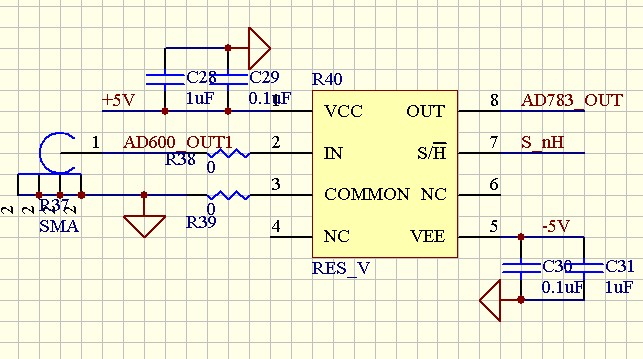

(原文件名:3.jpg)

采样使用采样保持放大器AD783,AD783快速的采样时间,高速的保持停留为采样系统提供了很高的吞吐率。AD783典型的建立时间为150ns,建立时间足够快,可以让SHA在不需求附加延时的情况下直接驱动AD转换器。

(原文件名:4.jpg)

4. AD数据转换电路

AD转换模块使用的是AD8721芯片,将从AD783采样保持放大器中发送来的模拟数据转换位8位数字信号传给FPGA进行处理。

5. 方波校准信号

由FPGA直接给出3.3V的100KHz方波信号,在外部进行电阻分压处理,就得到了幅值0.3V的方波校准信号。

软件设计与仿真

(原文件名:5.jpg)

1. 实时采样模块:

在输入信号频率低于50KHz时采用此模块进行信号采样,触发信号有效时便以1M的速率开始采样,在“单次触发模式”下只采集200个点,在连续触发模式下进行连续采样。

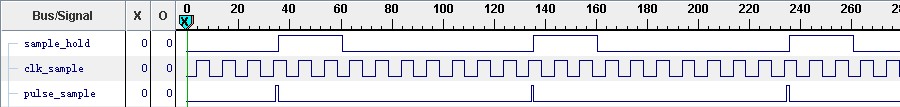

仿真波形如下:

(原文件名:6.jpg)

结果分析: 以1M的采样时钟产生脉冲宽度为100ns的采样脉冲,以采样脉冲为基准产生采样/保持电路的控制信号,一周期内高电平保持250ns进行采样,低电平保持750ns进行保持。此时序是完全可以让采样保持芯片正常工作的。

2. 等效采样模块:

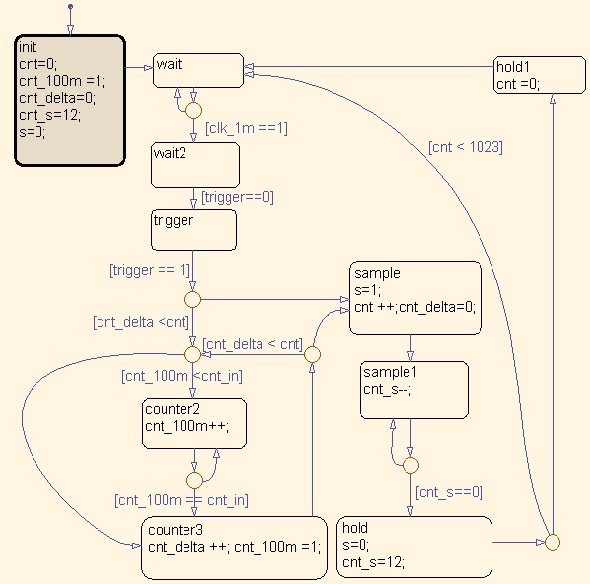

在输入信号频率高于50KHz时采用等效采样进行信号采集,以1M的速率对输入信号的一个周期采样一次,采样足200个点完成一屏的输出。此模块主要功能由状态机实现。

(原文件名:7.jpg)

结果分析: 触发信号为1M频率,仿真使用每屏32个采样点,在cnt的循环控制下每次的采样脉冲与触发信号的间隔逐渐增大,并呈循环的规律。输出的“sample_hold”采样-保持脉冲便是由密到疏的循环发生。

以下波形的△t为一个100m时钟周期,因此此次仿真的等效采样率为100MHz。

理论分析与计算

1.等效采样分析;

等效采样分为随即采样和顺序采样。在本方案中采用顺序等效采样方式,在PFGA的控制下,以1M的取样速率可得到200M甚至以上的带宽,并且在垂直分辨率上也可达到8bit以上。这种采样方式每个采样周期在波形上只取一个点,每次延迟一个已知的△t时间,△t可程序控制调整时宽,这样便可实现采样率的可调。下图为取样原理图:

(原文件名:8.jpg)

2. 垂直灵敏度

因为数字芯片的管脚输入电压由限,不能直接输入大信号,而太小的也容易被噪声干扰或者无法被识别,所以设计了衰减电路和增益电路对信号进行处理,以使能测量的电压范围尽可能的大。

当选择1V/div档时,最大电压8V,必须通过衰减电路进行1/10衰减后才能送入采集和处理电路,0.8V的信号经过AD600的2倍放大后Vpp为1.6V,送入采样比较器和AD处理。

选择0.1 V/div档时,输入最大电压0.8V,不需要经过衰减,送入AD600两倍放大后进行处理。

选择2mV/div档时,最大的满屏电压才16mv,AD600对信号进行100倍放大,输出0.16V送DA进行转换处理。

垂直灵敏度由外部拨动开关手动调整,由继电器网络选通不同的放大通道,满足题目的基本要求以及发挥要求中的三个档位。

实际测试结果如下:

输入信号Vpp/2 2V 1V 0.4V 0.2V 40mV

垂直灵敏度 1V/div 1V/div 0.1V/div 0.1V/div 2mV/div

测试值 1.97V 1.10V 0.39V 0.2V 41mv

误差 1.5% 1% 2.5% 0 2.5%

3. 扫描速度

扫描速度由FPGA根据需求进行在线调整,即根据档位的选择,改变采样的等效速率使采样点符合设定的时间间隔,存入RAM后直接输出,即保证了波形质量又能减少延时。FPGA的最小时钟间隔为10ns,在等效采样模式下用最小时间间隔计△t的宽度,可以在200ns/div~2us/div档位间任意调整,而在实时采样模式下可以到20ms/div,这样就满足了题目的要求。

实际测试结果如下:(测试条件: 垂直灵敏度 0.1V/div)

100ns 2us 1ms 20ms

扫速/div 100ns/div 2us/div 自动档 20ms/div

周期数 10 10 10.1 10.2

误差 0 0 1% 2%

4. 测试结论:

在垂直灵敏度和扫描速度方面都能达到基本和发挥中要求的档位和误差,其中垂直灵敏度调节由于经过衰减和增益电路,误差较大。而扫描速度是直接由FPGA控制,误差非常小。由于在FPGA中我们设置了频率计,可以做到另以个自动扫描档,自动根据输入的信号频率转换到合适的扫描速度。

等效采样VHDL程序代码:

--------------------------------------------------------------------------------

-- Company:

-- Engineer:

--

-- Create Date: 13:32:35 09/02/07

-- Design Name:

-- Module Name: s_h_test - Behavioral

-- Project Name:

-- Target Device:

-- Tool versions:

-- Description:

--

-- Dependencies:

--

-- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

--

--------------------------------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

---- Uncomment the following library declaration if instantiating

---- any Xilinx primitives in this code.

library UNISIM;

use UNISIM.VComponents.all;

entity s_h_test is -- 等效采样,包括控制7821及783,得到最终的输入信号

port (

clk_in: in std_logic;

clk_10m : in std_logic;

d_from_trigger : in std_logic;

int_ad_L : in std_logic;

din : in std_logic_vector(7 downto 0);

rst : in std_logic;

cnt_in : in integer;

read_ram : out std_logic;

wr_ad_L : out std_logic;

r_ad_L : out std_logic;

dout: out std_logic_vector(7 downto 0);

-- wea_ram : out std_logic;

-- cnt_out :out std_logic_vector(7 downto 0);

sH_hL : out std_logic

);

end s_h_test;

architecture Behavioral of s_h_test is

signal pulse_1m,d_from_trigger_d,pulse_1m_d : std_logic;

signal int_ad_L_d: std_logic;

signal din_d :std_logic_vector(7 downto 0);

signal state_clk1m_next: std_logic;

signal cnt_clk1m : integer range 0 to 100;

signal cnt_in_r : std_logic_vector(9 downto 0);

signal clk : std_logic;

--signal state_next : integer range 0 to 7;

--signal cnt_r : integer range 0 to 255;

--signal cnt_trigger: integer range 0 to 20;

--signal state_ad_next : std_logic_vector (1 downto 0);

signal dout_sample: std_logic_vector(7 downto 0);

signal clk_r_ram_dengxiao: std_logic;

signal addr_dengxiao_out: std_logic_vector(7 downto 0);

signal state_r_ram_dengxiao: integer range 0 to 1;

signal read_ram_d_dengxiao: std_logic;

signal cnt_out: std_logic_vector(7 downto 0);

signal wea_ram: std_logic;

COMPONENT d_sample

PORT(

trigger : IN std_logic;

int_ad_L : IN std_logic;

din : IN std_logic_vector(7 downto 0);

clk_1m : IN std_logic;

cnt_in : IN std_logic_vector(9 downto 0);

ce : IN std_logic;

clk : IN std_logic;

reset : IN std_logic;

cnt : OUT std_logic_vector(7 downto 0);

s : OUT std_logic;

wr_ad_L : OUT std_logic;

read_ram : OUT std_logic;

din_r : OUT std_logic_vector(7 downto 0);

r_ad_L : OUT std_logic;

wea_ram : OUT std_logic

);

END COMPONENT;

component dengxiao_ramm IS

port (

addra: IN std_logic_VECTOR(7 downto 0);

addrb: IN std_logic_VECTOR(7 downto 0);

clka: IN std_logic;

clkb: IN std_logic;

dina: IN std_logic_VECTOR(7 downto 0);

doutb: OUT std_logic_VECTOR(7 downto 0);

wea: IN std_logic);

END component;

begin

clk <= clk_in;

Inst_d_sample: d_sample PORT MAP(

cnt => cnt_out,

s => sH_hL,

wr_ad_L => wr_ad_L,

wea_ram => wea_ram,

read_ram => read_ram_d_dengxiao,

trigger => d_from_trigger_d,

int_ad_L => int_ad_L_d,

din => din_d,

din_r => dout_sample,

clk_1m => pulse_1m_d,

cnt_in => cnt_in_r,

ce => '1',

clk => clk,

r_ad_L => r_ad_L,

reset => rst

);

read_ram <= read_ram_d_dengxiao;

cnt_in_r <= conv_std_logic_vector (cnt_in,10) ;

clk_r_ram_dengxiao <= clk_10m;

inst_dengxiao_ramm: dengxiao_ramm

port map(

addra => cnt_out,

addrb => addr_dengxiao_out,

clka => clk,

clkb => clk_r_ram_dengxiao,

dina => dout_sample,

doutb => dout,

wea => wea_ram);

process(clk_r_ram_dengxiao,rst) --ram

begin

if rst = '1' then

addr_dengxiao_out <= (others=>'0');

elsif clk_r_ram_dengxiao'event and clk_r_ram_dengxiao = '1' then

case state_r_ram_dengxiao is

when 0 =>

addr_dengxiao_out <= (others=>'0');

if read_ram_d_dengxiao = '1' then

state_r_ram_dengxiao <= 1;

end if;

when 1 =>

if addr_dengxiao_out = 200 then

state_r_ram_dengxiao <= 0;

else

addr_dengxiao_out <= addr_dengxiao_out + 1;

end if;

when others => null;

end case;

end if;

end process;

process(clk) --时钟同步寄存器!!

begin

if clk'event and clk = '1' then

d_from_trigger_d <= d_from_trigger;

pulse_1m_d <= pulse_1m;

int_ad_L_d <= int_ad_L;

din_d <= din;

end if;

end process;

process(clk_10m,rst) -- 生成1MHz的采样脉冲 pulse_1m (有修改)

begin

if rst = '1' then

cnt_clk1m <= 0;

pulse_1m <= '0';

state_clk1m_next <= '0';

elsif clk_10m 'event and clk_10m ='1' then

case state_clk1m_next is

when '0' =>

pulse_1m <= '1';

state_clk1m_next <= '1';

when '1' =>

pulse_1m <= '0';

if cnt_clk1m = 8 then

state_clk1m_next <= '0';

cnt_clk1m <= 0;

else

cnt_clk1m <= cnt_clk1m + 1;

end if;

when others => null;

end case;

end if;

end process;

end Behavioral; |

阿莫论坛20周年了!感谢大家的支持与爱护!!

如果天空是黑暗的,那就摸黑生存;

如果发出声音是危险的,那就保持沉默;

如果自觉无力发光,那就蜷伏于牆角。

但是,不要习惯了黑暗就为黑暗辩护;

也不要为自己的苟且而得意;

不要嘲讽那些比自己更勇敢的人。

我们可以卑微如尘土,但不可扭曲如蛆虫。

|