|

|

楼主 |

发表于 2009-4-29 19:16:02

|

显示全部楼层

先谢谢仙猫,不过还是有很多地方需要说明一下:

1、前几张图看不出有明显的毛刺。

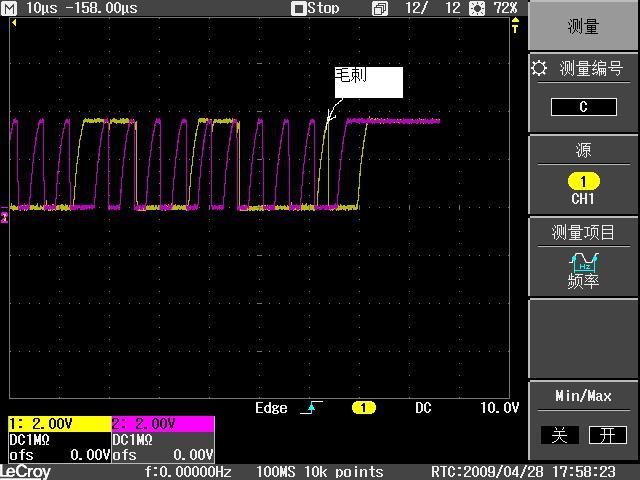

前几张的毛刺放大图都和最后一张差不多,很多毛刺的峰值都已经达到了i2c通信的高电平值了,毛刺我在图上标注了下,又传了上来。

2、只用内置上拉信号时虽上升的时间较缓,但能升到顶,看不出存在会造成出错波形。

上边的图中都有时间信息,大概估算了一下,这种情况下SDA 和SCL 信号的上升时间需要3us,即3000ns,已经远远超出了i2c总线规定的1000ns(这是标准模式下的最大值,快速模式下是300ns)。

需要说明的是这种通信是能够持续一段时间的,多则一两个小时,少则几分钟,很随机。不明所以。

3、问题是最后一张图里的毛刺(SCL?),会不会是软件bug?比如存在重新设置端口的语句。(即使没动该位,但若同一端口的其他位设置时,不小心也操作了该位,等等……)

软件编写是按avr数据手册来的,几乎都是按照手册上的实例代码写的,并且仅仅是对i2c的测试,并没有调用其它功能模块,还有一点需要说明的是当我接了外接上拉电阻之后,毛刺明显增多,代码并没有改变,应该不是软件的问题吧。

放大了会很明显 (原文件名:SCRN0194-1.JPG)

使用内部上拉的毛刺标注 (原文件名:SCRN0195-1.JPG) |

|