|

|

寄存器配置如下

#define FSCTRL1 0x0B //0x08 // FSCTRL1 Frequency synthesizer control.

#define FSCTRL0 0x00 // FSCTRL0 Frequency synthesizer control.

#define FREQ2 0x10 //0x21 // FREQ2 Frequency control word, high byte.

#define FREQ1 0xA7 //0x65 // FREQ1 Frequency control word, middle byte.

#define FREQ0 0x62 //0x6A // FREQ0 Frequency control word, low byte.

#define MDMCFG4 0x2D //0x5B // MDMCFG4 Modem configuration.

#define MDMCFG3 0x3B //0xF8 // MDMCFG3 Modem configuration.

#define MDMCFG2 0x73 // MDMCFG2 Modem configuration.

#define MDMCFG1 0x22 // MDMCFG1 Modem configuration.

#define MDMCFG0 0xF8 // MDMCFG0 Modem configuration.

#define CHANNR 0x00 // CHANNR Channel number.

#define DEVIATN 0x00 //0x47 // DEVIATN Modem deviation setting (when FSK modulation is enabled).

#define FREND1 0xB6 // FREND1 Front end RX configuration.

#define FREND0 0x10 // FREND0 Front end RX configuration.

#define MCSM0 0x18 // MCSM0 Main Radio Control State Machine configuration.

#define FOCCFG 0x1D // FOCCFG Frequency Offset Compensation Configuration.

#define BSCFG 0x1C // BSCFG Bit synchronization Configuration.

#define AGCCTRL2 0xC7 // AGCCTRL2 AGC control.

#define AGCCTRL1 0x00 // AGCCTRL1 AGC control.

#define AGCCTRL0 0xB2 // AGCCTRL0 AGC control.

#define FSCAL3 0xEA // FSCAL3 Frequency synthesizer calibration.

#define FSCAL2 0x0A // FSCAL2 Frequency synthesizer calibration.

#define FSCAL1 0x00 // FSCAL1 Frequency synthesizer calibration.

#define FSCAL0 0x11 // FSCAL0 Frequency synthesizer calibration.

#define FSTEST 0x59 // FSTEST Frequency synthesizer calibration.

#define TEST2 0x88 // TEST2 Various test settings.

#define TEST1 0x31 // TEST1 Various test settings.

#define TEST0 0x0B // TEST0 Various test settings.

#define IOCFG2 0x0B // IOCFG2 GDO2 output pin configuration.

#define IOCFG0 0x06 // IOCFG0 GDO0 output pin configuration.

#define PKTCTRL1 0x04 // PKTCTRL1 Packet automation control.

#define PKTCTRL0 0x05 // PKTCTRL0 Packet automation control.

#define ADDR 0x00 // ADDR Device address.

#define PKTLEN 0xFF // PKTLEN Packet length.

// PATABLE (0 dBm output power)

INT8U PaTabel[8] = {0xC0 ,0xC0 ,0xC0 ,0xC0 ,0xC0 ,0xC0 ,0xC0 ,0xC0};

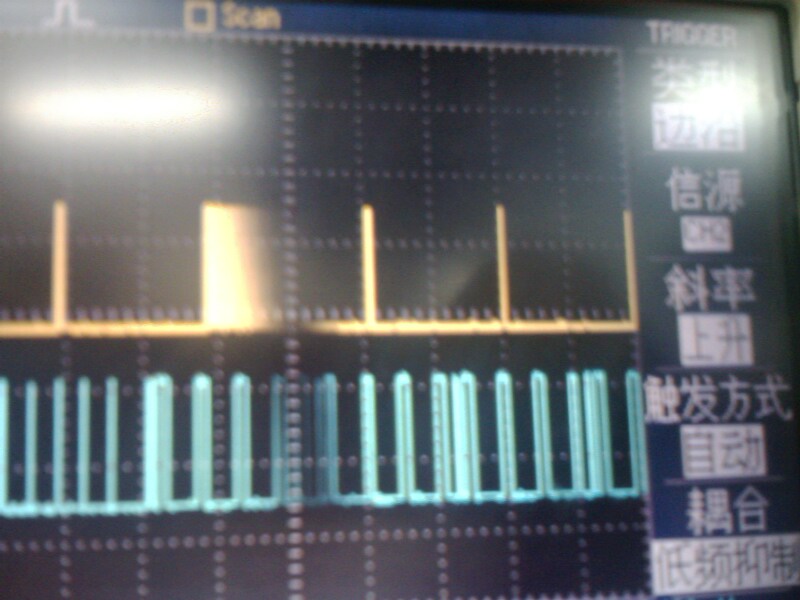

GDO0脚设置0x06,在观察接收和发发送的GDO0脚时如图一,这样的波形是不是代表有接收??但是接收端在写寄存器的时候是有跳变的,我怀疑这些等间隔的跳变是写寄存器的时候引发的,因为接收不到正确的数据包.(我在单步执行程序的时候发现,到写配置寄存器时GDO0是有跳变的这是否不正常?)

GDO0脚收发时的电平变化.蓝色发,黄色收 (原文件名:IMG0325A.jpg)

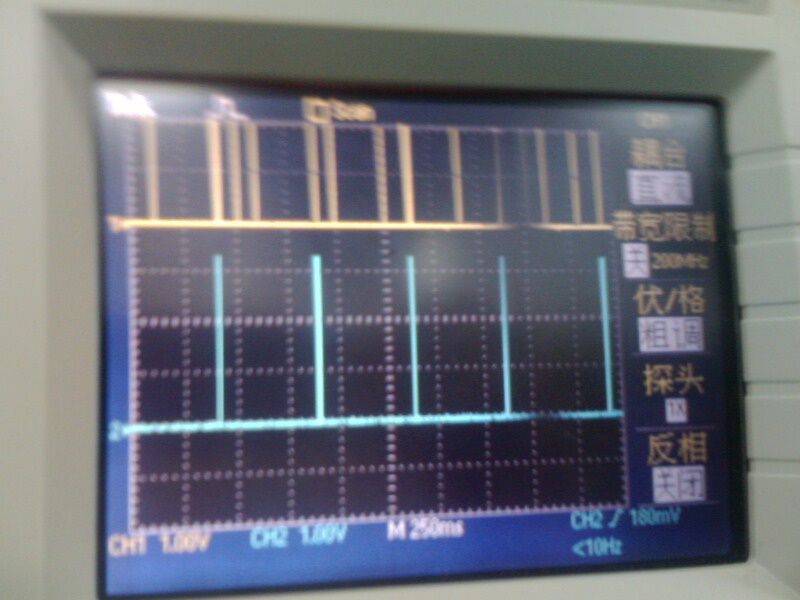

我在芯片的RF端也测过,跟GDO0脚相似,收发也没有等间隔.而且有点杂乱无章.

芯片RF端信号.黄色发,蓝色收 (原文件名:IMG0326A.jpg)

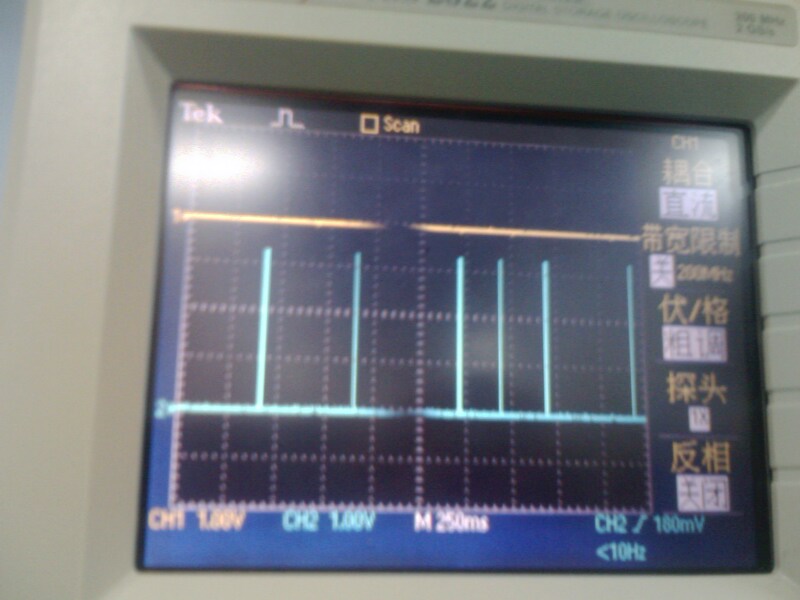

最匪夷所思的是我在芯片RF测的时候故意关掉了发送机,但是接收机居然能够收到信号.不知道是怎么回事

RF端信号, 没有发送的时候居然还有收 (原文件名:IMG0327A.jpg)

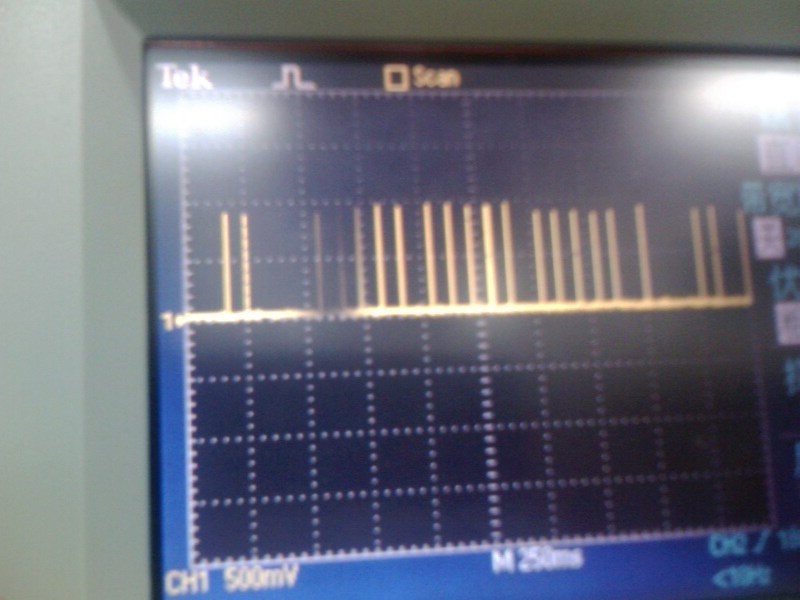

这是单独的发送

RF端发送 (原文件名:IMG0328A.jpg)

这是单独的接收

RF端接收 (原文件名:IMG0329A.jpg) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|