|

|

展会捡来的灯条,UCS2903串行控制,800K传输速率,归零码。

1us高电平+0.25us低电平表示“1”,0.25us高电平+1us低电平表示“0”.

想用FPGA的GPIO的IP来模拟归零码,但是S3E的GPIO口电平反转一次要980ns,速率不够。

我的设想就是在gpio口外接一个归零码的译码器,

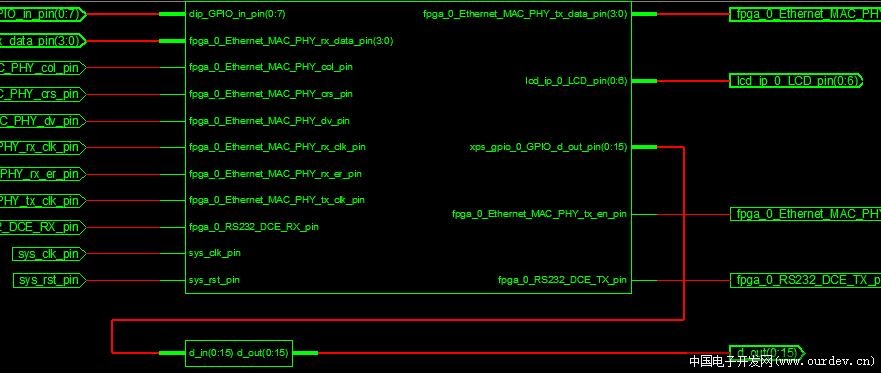

顶层模块包含一个MB核的子模块,向GPIO输出数据,输出间隔1.25us。

还有一个译码器模块,将GPIO的输出作为敏感输入信号,输出1.25us的归零码。

模块的RTL图 (原文件名:rtl.JPG)

MB模块通过GPIO输出一个固定值num = 0xaaaa,间隔1.25us num值取反输出,循环……

译码器模块检测到GPIO信号变化,先输出高电平,延迟0.25us,再根据输入端口的值输出,延迟0.75us,再输出低电平

module rz_recoder(d_in, d_out

);

input [0:15] d_in;

output [0:15] d_out;

reg [0:15] temp;

assign d_out = temp;

always @ (d_in[0])

begin

temp = 16'hffff;//输出高电平

#250;//延迟250ns

temp = d_in;//输出数据

#750;//延迟750ns

temp = 16'h0000;//输出低电平

end

endmodule

综合过后下载到开发板,没有输出,用逻辑分析仪看到的都是一些无规律的波形。

查看RTL图,译码模块被综合成GND了。。。= =

单独把译码模块拿出来仿真波形却是对的,

把begin end中间的代码去掉,写成temp = ~d_in;综合出来的译码器就是一个反向器,下载后波形正常0xaaaa和0x5555间隔1.25us交替出现.

求助这个译码模块怎么写,EDK和ISE联合设计第一次搞。。。。。。求指导。 |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|