|

|

在EDK定制用户IP需要调用ISE生成的IP,在网上搜索了解决方案如下,

在ISE中封装HDL,并使用IP,设计分三大步:

第一步:像通常建立工程设计一样,先编写一个模块,如:

module add(a,b,c)

Input a,b;

output[1:0]

assign c=a+b;

endmodule

设置综合选项,综合过程中不能加入IO buf和iob(考虑到跟外部模块接口问题):

在综合设置中,-iobuf不要勾选,-iob选 NO,综合,生成网表add.ngc;

第二步:制作一个blackbox模块(就是一个IP的wrapper封装设计),如下:

module add(a,b,c)

input a,b;

output[1:0]

endmodule

只申明端口。

第三步:使用此IP,需要先把第二步的blackbox以v文件形式加入到工程,再调用这个模块,再把add.ngc文件加入到工程文件夹下即可(注意此过程在综合实现时候,要把第一步的两个选项选上)。

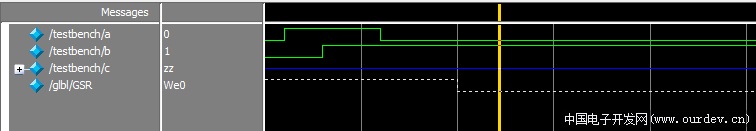

按照以上的步骤建立工程,然后在modelsim测试发现输出C一直是高阻态,感觉像是第一步生成的网表没有加进去,斑竹知道这里面哪一步有问题吗

testbench.v

module testbench;

// Inputs

reg a;

reg b;

// Outputs

wire [1:0] c;

// Instantiate the Unit Under Test (UUT)

ip_test uut (

.a(a),

.b(b),

.c(c)

);

initial begin

// Initialize Inputs

a = 0;

b = 0;

// Wait 100 ns for global reset to finish

#10 a=1;

b=0;

#20 a=1;

b=1;

#30 a=0;

b=1;

#200 $stop;

// Add stimulus here

end

endmodule

(原文件名:QQ截图20111113131821.png) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|