|

|

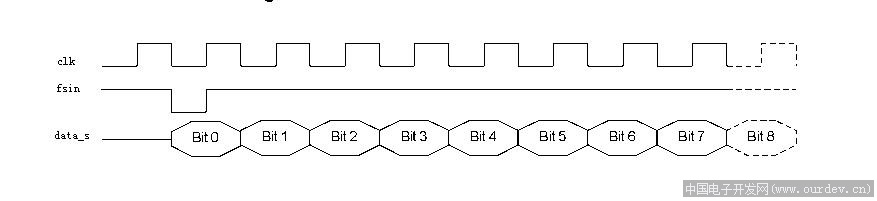

//此为某个串行通信协议,clk、fsin、data_s均为输入信号,data_p为并行输出数据,数据位数为8。通信协议如下图所示。硬件描述语言如下。

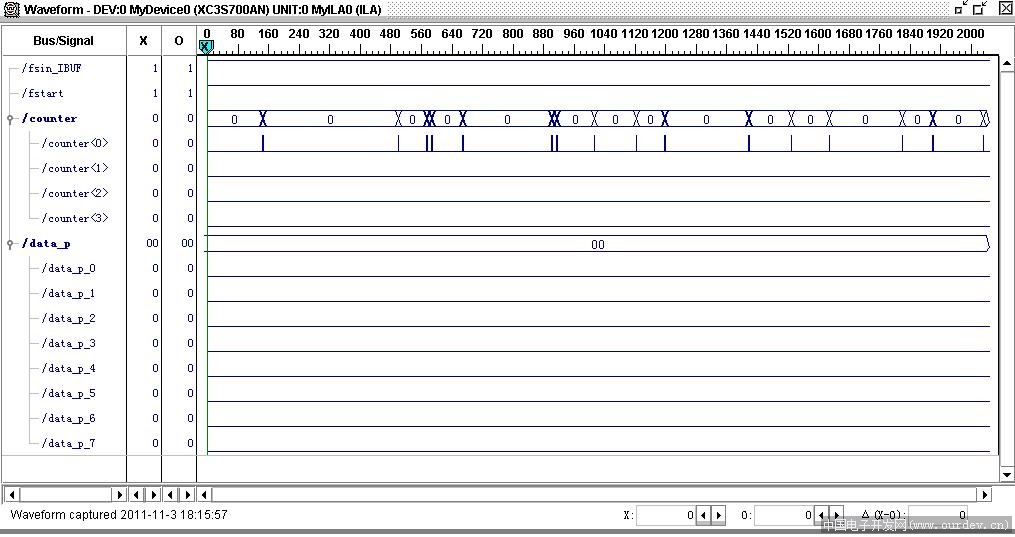

//出现的问题是:counter不能计数到8,因此未能将全部数据捕获。请教各位,为什么会出现这种问题,怎样解决这个问题?谢谢……

//代码在附件中。

module tdm(clk,fsin,data_s,data_p);

input clk,fsin,data_s;//串行输入信号

output [7:0] data_p;//并行输出数据

reg [7:0] data_p;

reg fstart;//开始标志

reg [7:0] data;

reg [3:0] counter;//计数用,在接收到一个数据时加1。

initial begin

fstart <= 0;

counter <= 0;

data <= 0;

end

always @(posedge clk or negedge fsin)begin

if(~fsin)begin

fstart <= 1;//fsin的下降沿,开始标志置位。

counter <= 0;//计数器清零

end

else begin

if(fstart==1 && counter<8)begin//开始标志有效,计数个数小于8,则将数据置入data[counter],同时counter自加1.

data[counter] <= data_s;

counter<=counter+1;

end

if(counter==8)begin

data_p[7:0] <= data[7:0];//计数个数为8个,输出数据。

fstart<=0;//开始标志复位

counter<=0;

end

end

end

endmodule

代码ourdev_691406NQ40YA.rar(文件大小:684K) (原文件名:tdmfinal1.rar)

通信协议时序图 (原文件名:通信协议.JPG)

chipscope 时序图 (原文件名:chipscope.JPG) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

知道什么是神吗?其实神本来也是人,只不过神做了人做不到的事情 所以才成了神。 (头文字D, 杜汶泽)

|