|

|

module xulie(

clk,

rst_n,

in,

out

);

input clk,rst_n,in;

output reg out;

//01101

reg [2:0] state,next_state;

parameter idle=3'd0;//

parameter s1=3'd1;//0

parameter s2=3'd2;//01

parameter s3=3'd3;//011

parameter s4=3'd4;//0110

parameter s5=3'd5;//01101

always @ (posedge clk or negedge rst_n)

if(!rst_n)

state<=idle;

else

state<=next_state;

always @ (state or in)

begin

next_state=3'bxxx;

case(state)

idle:if(in==0)

next_state=s1;

else

next_state=idle;

s1:if(in==1) //0

next_state=s2;

else

next_state=s1;

s2:if(in==1) //01

next_state=s3;

else

next_state=s1;

s3:if(in==1) //011

next_state=idle;

else

next_state=s4;

s4:if(in==1) //0110

next_state=s5;

else

next_state=s1;

s5:if(in==1) //01101

next_state=s3;

else

next_state=s1;

default:next_state=idle;

endcase

end

always @ (state)

case(state)

idle,s1,s2,s3,s4:out<=1'b0;

s5:out<=1'b1;

default:out<=1'b0;

endcase

endmodule

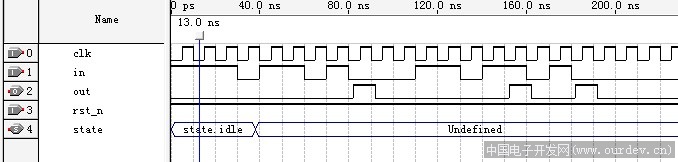

这是一个简单的检测01101序列的程序,进行后仿真的时候,发现idle之后的状态全部是undefined,但是程序依然能正确输出。

这是怎么一回事?

有一个警告:Warning: Can't display state machine states -- register holding state machine bit "|xulie|state.idle" was synthesized away

我F1了一下,大概意思就是状态被综合掉 。

请大家看看是怎么回事,

如果用功能仿真的话就没这种问题

(原文件名:FM(VWSLHF{5E4N0ICMB%J]X.jpg) |

阿莫论坛20周年了!感谢大家的支持与爱护!!

曾经有一段真挚的爱情摆在我的面前,我没有珍惜,现在想起来,还好我没有珍惜……

|